Other Parts Discussed in Thread: LM5067

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号: LM5067

您好:

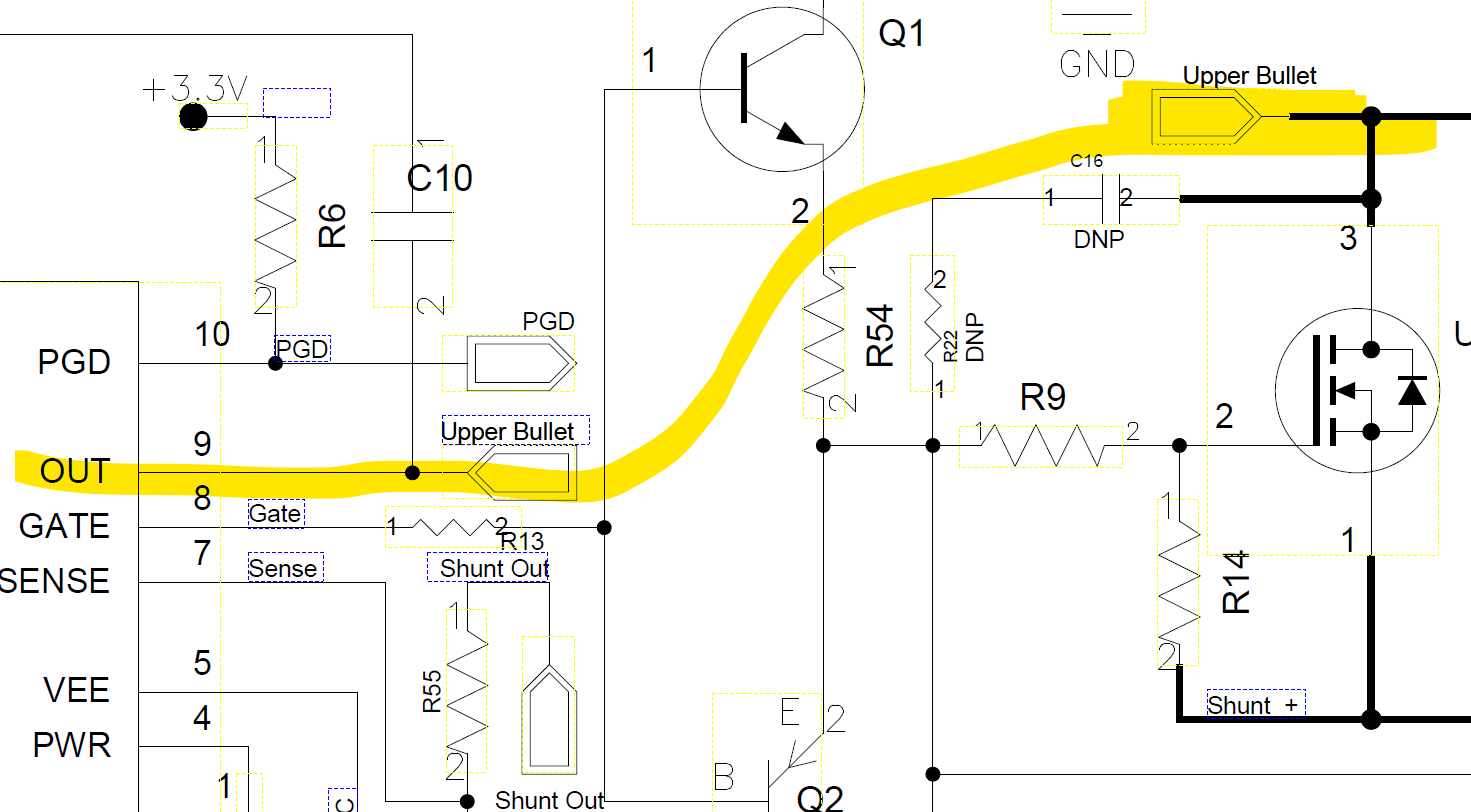

我正在设计一个电路、按照数据表中的建议将 MOSFET 的漏极连接到 LM5067 的 OUT 引脚。

已连接基准电路。

我观察到的情况是

- 我的负载(纯电阻)未打开、直到 I Disconnect Load、并在开启后重新连接(需要打开电路,然后需要连接负载)

- 在任何故障情况(即 UV、OV、Overload、使用 EN 处的晶体管彻底截断)期间、它会关闭、但不会自动重启(根据观察计时器引脚上的波形,我知道它在 8 个周期后变为 0.3V,但不会重启,卡在同一个环路中)

解决方案我要做的是断开负载并需要连接。 - 当我与 LM5067 的 OUT 引脚断开 MOSFET 的漏极引脚连接后、工作正常、但数据表再次指出需要在浪涌期间进行连接以实现软启动。

在这种情况下、任何人都能帮助我做些什么吗?

请告诉我是否有人需要更多详细信息来重新评级测试案例。