https://e2e.ti.com/support/logic-group/logic/f/logic-forum/582738/txs0104e-txs0104-question

部件号:TXS0104E大家好,

我有一个关于TXS0104E的问题,需要您的快速支持。

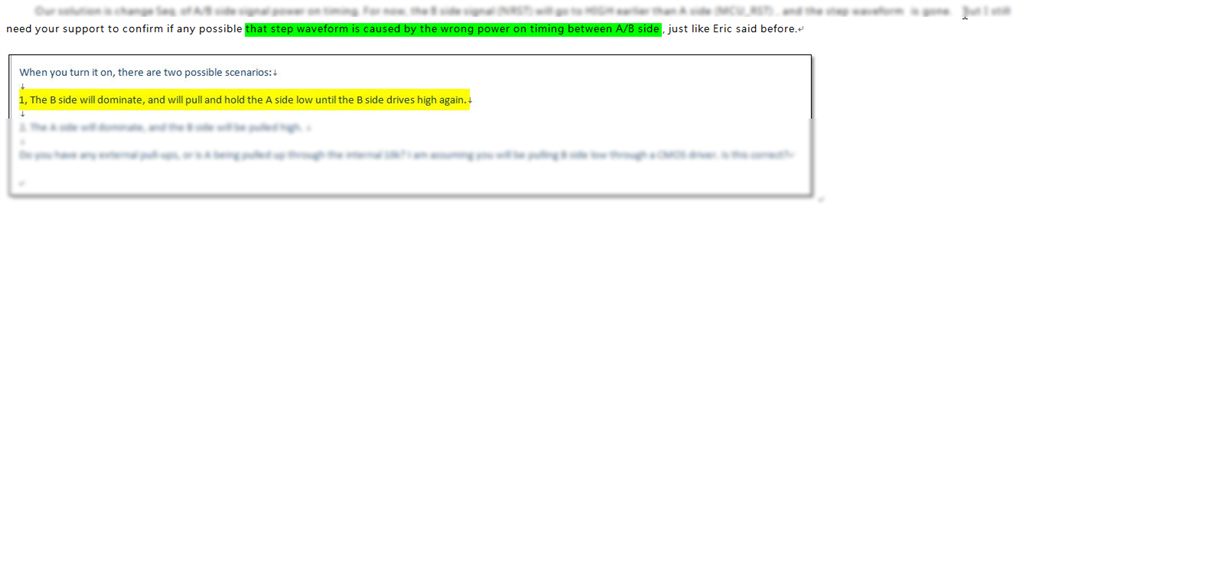

当TXS0104E A侧信号已从PU到High (高),但B侧信号仍保持低,,然后TXS0104E打开时,信号是否会短暂拉低(不是0V)几(毫秒),然后再次返回High (高)?

请参阅我们测量的以下波形,如果卸载TXS0104E,则看不到NRST步进上升延迟。 请给我一些意见,谢谢。