https://e2e.ti.com/support/logic-group/logic/f/logic-forum/662115/sn74aup1g17-frequency-limitations

部件号:SN74AUP1G17线程中讨论的其他部件: SN74AUP1G74, TINA-TI, SN74LVC1G17, SN74LVC1G14, SN74AUC1G17

大家好,

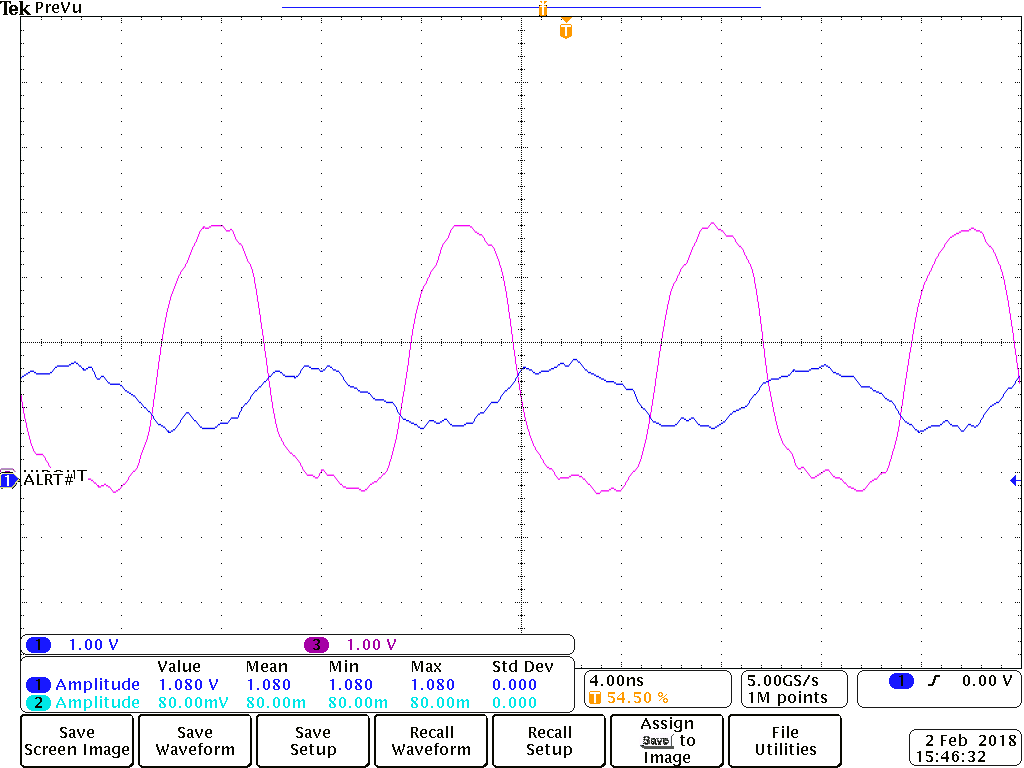

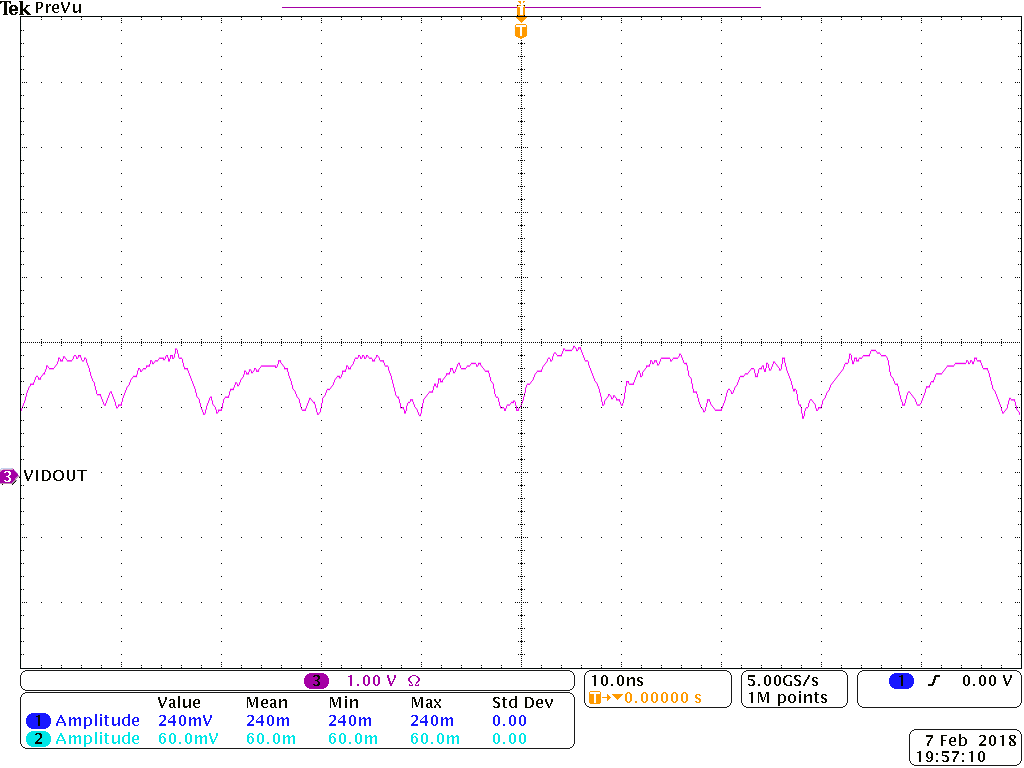

SN74AUP1G17是否能够通过它驱动100MHz时钟? 数据表中的哪些信息可用于确定频率限制(如果有)? 我的客户希望看到一个方形波形,但听起来好像他们看到了一个带有直流偏移的非方形波形。 设备在1.8V的电压下工作。 我要求提供波形的屏幕截图,但希望在此期间发布此问题。

如果SN74AUP1G17不支持100MHz,您可以推荐一个P2P设备吗? 软件包为SC70。

谢谢!

Joe Stephan - FAE