Other Parts Discussed in Thread: CD74HC165, SN74HC165, SN74HCS165, ISO7740

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1097589/sn74hc165-technology-discussion

部件号:SN74HC165主题中讨论的其他部件:CD74HC165, SN74HCS165, ISO7740

尊敬的:

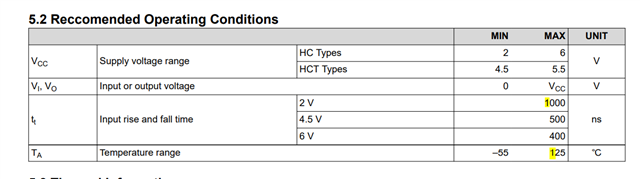

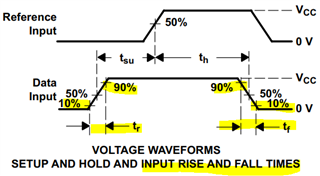

数据表注释2:当Vcc =2V时 ,TT =1000nS =1000nS /V x (1.5V-0.5V)? 如果Vcc=4.5V,TT= 500ns/V x (3.15 -1.35)=900ns,则芯片不会损坏。 只要低于1.35V或高于3.15V,是否安全?

如果没有,请帮忙解释,非常感谢~

Vcc=5V是否有参考值?