各位专家、您好。

客户中使用的是 SN74HC573A-Q1 、用于 BMS。 该项目属于 DV。 SN74HC573A-Q1存在故障输出、将导致整个系统停机。

此器件需要在9/10之前进行修复。 因此它可以捕获 PV 测试进度。

以下是此问题的描述:

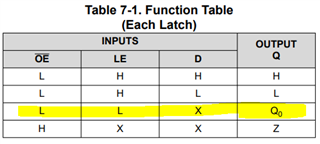

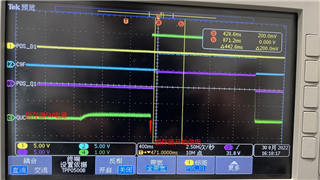

上电时、LE 和/OE 被下拉、输入(D)为低电平、 但有时输出为高电平。 我们发现、在上电之前、电源引脚为0.8V、这是由 MCU 引起的。 具有 相同器件的竞争对手不会出现此问题。 您能帮助解释这个问题吗? 谢谢。

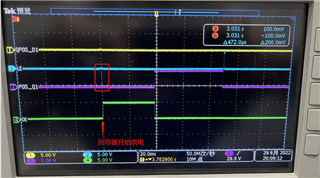

SN74HC573A-Q1的数据表中描述了/OE 需要在上电之前保持高电平、但在该系统中、它无法 满足此要求。 因为如果它们上拉/OE、则需要重新设计 PCB、并且我们的器件无法赶上 PV 时序。 我还让客户在电流板上执行测试(在5V 和/OE 之间飞 A 线、而 SN74HC573A-Q1由5V 电源供电)、它还具有针对/OE 和5V 的电源序列、可能导致故障输出。 当软件关闭 OE 电源时、输出仍然为高电平。 它还需要上拉 LE 和下拉 D1、此时 Q1通过 D1下拉。 但在软件上拉 LE 之前、初始化将发生故障。 您还能帮助解释一下吗? 为何在/OE 被下拉时 Q1为高输出? 谢谢。

此致

郭松珍