Other Parts Discussed in Thread: SN74LVC1G74, SN74LVC1G14, SN74HCS72

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1025764/function-support-consulting

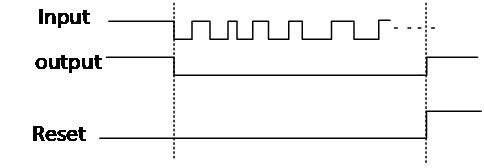

主题中讨论的其他器件:SN74LVC1G74、 SN74LVC1G14、 SN74HCS72客户希望检查是否有任何器件可支持以下功能。 它们期望输出在输入信号的第一个下降沿变为低电平、并且仅在复位信号变为高电平时恢复。