https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1025764/function-support-consulting

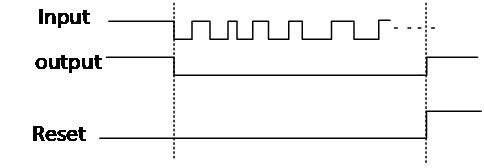

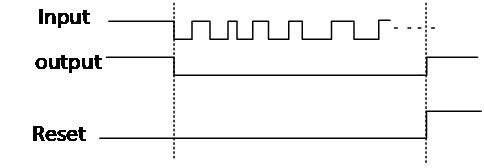

主题中讨论的其他器件:SN74LVC1G74、 SN74LVC1G14、 SN74HCS72客户希望检查是否有任何器件可支持以下功能。 它们期望输出在输入信号的第一个下降沿变为低电平、并且仅在复位信号变为高电平时恢复。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1025764/function-support-consulting

主题中讨论的其他器件:SN74LVC1G74、 SN74LVC1G14、 SN74HCS72客户希望检查是否有任何器件可支持以下功能。 它们期望输出在输入信号的第一个下降沿变为低电平、并且仅在复位信号变为高电平时恢复。

尊敬的 Aki:

我不确定这里的预期操作是什么。 下面是我认为显示的内容:

(1)如果输入在高电平状态下保持稳定、则输出保持在高电平状态。

(2)一旦输入切换为低电平、输出进入低电平状态、并保持该状态 、直到复位变为高电平。

(3)我的假设是、只要复位保持高电平、输出就会保持高电平

我同意 D 型触发器可用于此操作、并且将是最简单的解决方案-例如 SN74LVC1G74。

我要将输入信号连接到'1G74的 CLR\引脚、并通过逆变器(例如 SN74LVC1G14)将复位信号连接到 PRe\引脚。 D 和 CLK 可以端接至接地端、因为我认为它们对于这个电路来说不是真的必要的--至少如果我正确地理解了运行。