Other Parts Discussed in Thread: CD74HCT4511

主题中讨论的其他器件:CD74HCT4511

您好、专家、

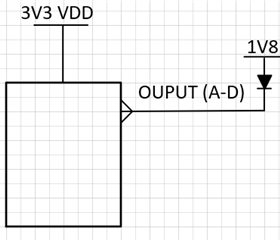

客户对 VDD 和模数转换引脚有疑问、 如果我们将 P3V3用于 VDD、并将1.8V 电压电平用于~D 引脚、是否需要将1.8V 电压转换为3.3V?

此致、

标记

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: CD74HCT4511

您好、专家、

客户对 VDD 和模数转换引脚有疑问、 如果我们将 P3V3用于 VDD、并将1.8V 电压电平用于~D 引脚、是否需要将1.8V 电压转换为3.3V?

此致、

标记

Mark、您好!

我有点困惑、您是否提到了类似这样的某种设置?

另外、正如 Clemens 所说、CD4000系列通常用于更高的工作范围。

CD74HCT4511中有一个类似的器件 、在这些较低的值下工作得更好。

此致、

Owen

大家好、Owen、

根据客户的要求,他们需要解码器支持0~F 显示,因此他们 不会使用 CD74HCT4511。

但 它们是 BCD GPIO (1.8V 至3.3V)原理图中的电平位移、请帮助在第9页中查看、如下文件所示。

e2e.ti.com/.../vistara_5F00_1004_5F00_1100_5F00_Review.pdf

CD4056BPW 有一些问题:

对此,

标记