主题中讨论的其他器件: TPS3808、 TLV803E

您好!

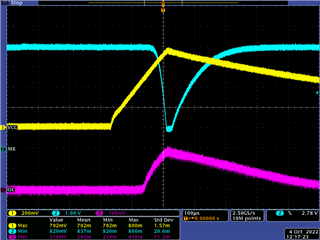

我们在设计中使用的是 SN74LVC1G126YZPR。 我们观察 到在上电时 SN74LVC1G126输出上出现意外毛刺脉冲、这会触发下电上电周期、从而影响电路板。

我们期望输出在加电时处于高阻抗状态。 不过、我们观察到、加电时 、SN74LVC1G126会将输出拉低大约50秒。

根据 SN74LVC1G126数据表" 为了确保加电或断电期间的高阻抗状态、OE 应通过一 个下拉电阻器接至 GND;"

我们已将 OE 引脚连接到上电时的1K 下拉电阻器。 它还连接到 TI 74LVC1G74DC 触发器 Q 输出。 加电时、74LVC1G74DC 输出上升至大约220mV。

SN74LVC1G126被连接至一个触发电源循环的 TPS3808 MR 复位输入。 因此、我们希望避免 在加电时 SN74LVC1G126上出现毛刺脉冲。

- 请告知 是否有某种方法可以避免 SN74LVC1G126在加电时出现这种毛刺脉冲。

我已附加原理图电路以及 SN74LVC1G126 Y 输出、VCC 和 OE 上电时的波形。 (请注意、在波形中、Y 输出标记为 MR (手动复位))

谢谢

路易