Other Parts Discussed in Thread: SN74LVC2G07

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1011551/sn74lvc2g07-glitch-consult

器件型号:SN74LVC2G07大家好、

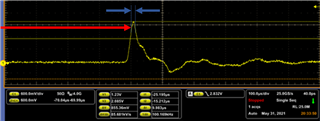

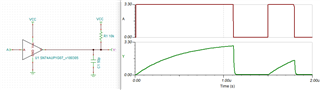

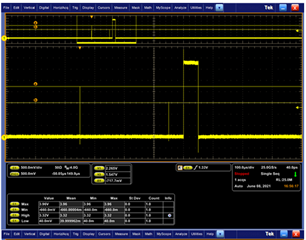

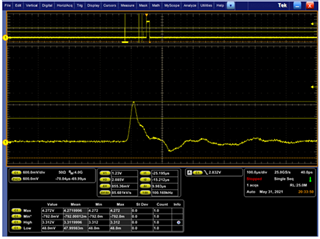

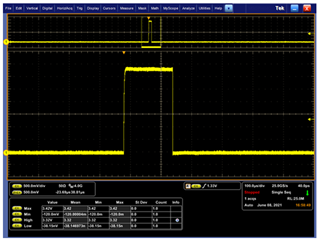

您能在下面看到问题描述吗? 随附了详细的波形屏幕截图。 谢谢

- 客户发现 IC 输入端存在串扰干扰、但输出端没有尖峰。 他们想知道串扰干扰可能导致 IC 输出错误的条件。 您可以在此处看到一些尖峰达到 VIH (2V)。

最棒的

斯坦利