请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74ACT244 大家好、

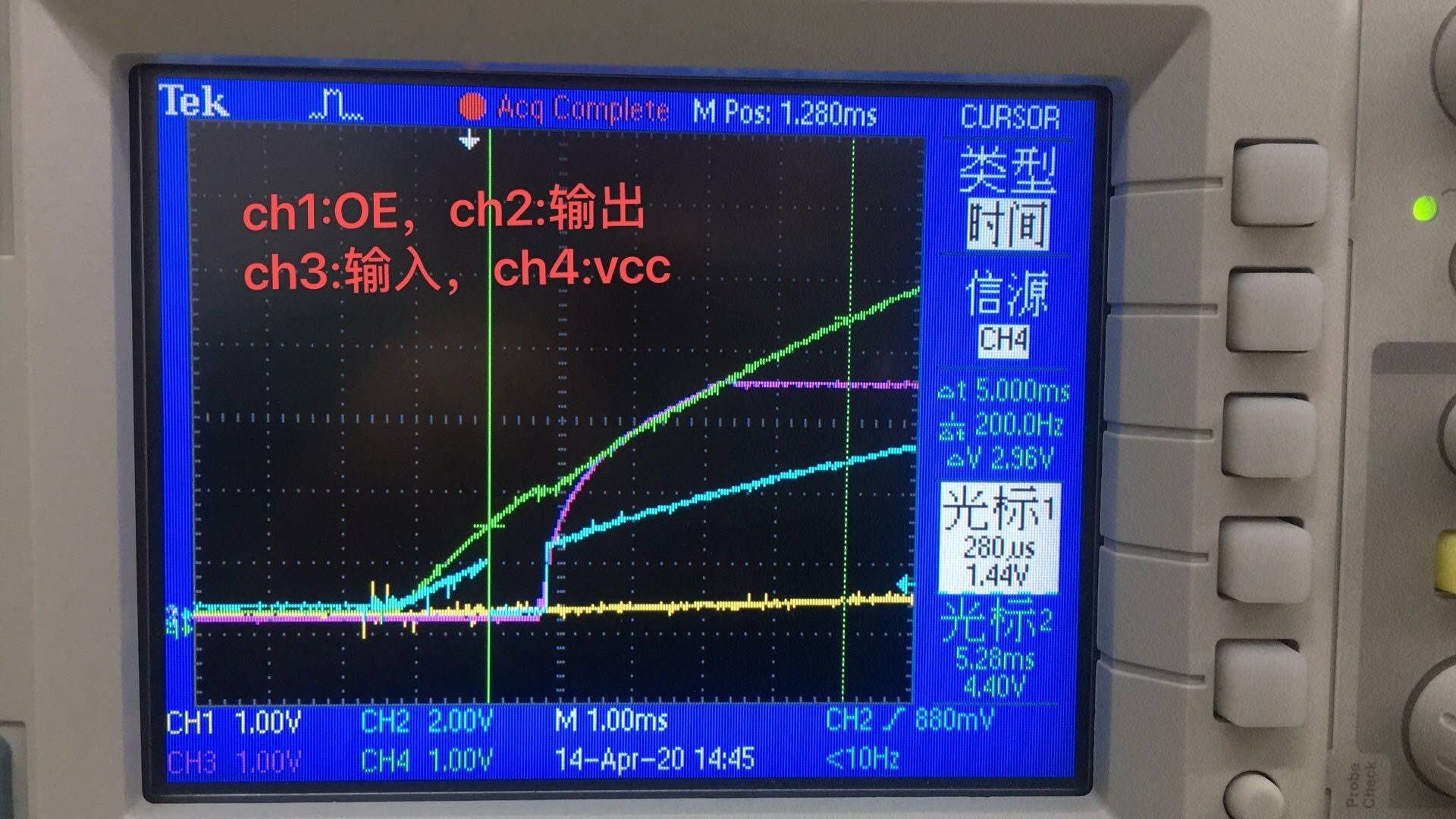

我的客户正在测试 SN74ACT244。 当整个系统处于加电状态时、我们捕获了以下波形:

CH1:OE。 OE 始终为0V

通道2:输出。

- 当 VCC 从0V 上升时、输出将跟随 VCC 上升

- 当 VCC 达到~1.5V 时、输出下降至0V

- 当输入信号开始上升时、输出开始跟随输入信号上升。

通道3:输入。 输入来自 C2000 GPIO

CH4:VCC 电源

因此、未经稳压的输出信号将触发一些不必要的操作。 那么、您能否帮助检查如何在加电期间避免此问题?

此致、

韦恩