请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74AVCH2T45 主题中讨论的其他器件: SN74AXC2T45

大家好、

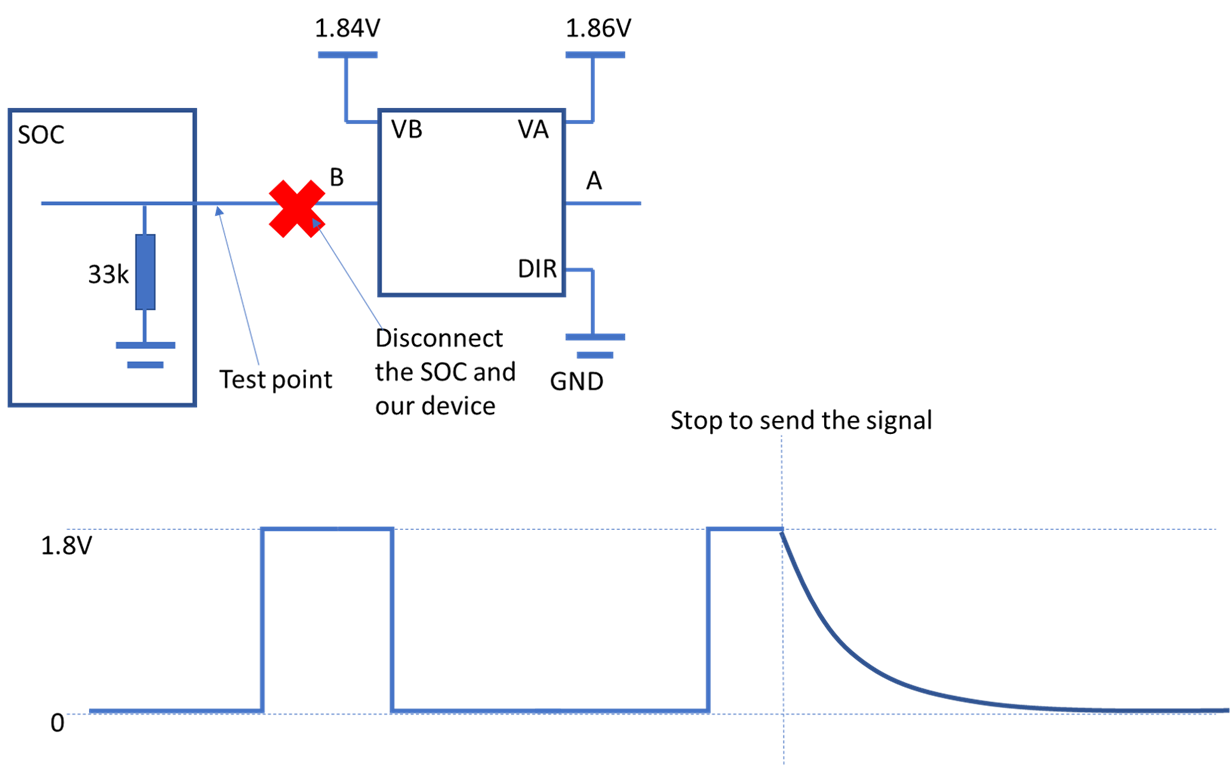

我的客户对 SN74AVCH2T45有一个问题。 有一个内部33k 下拉电阻器。 当输出为高电平时、它们停止发送信号。 如果它们断开其 SOC 和我们的芯片、则测试点的电压可以返回0V。 因此 SOC 应该可以正常工作。

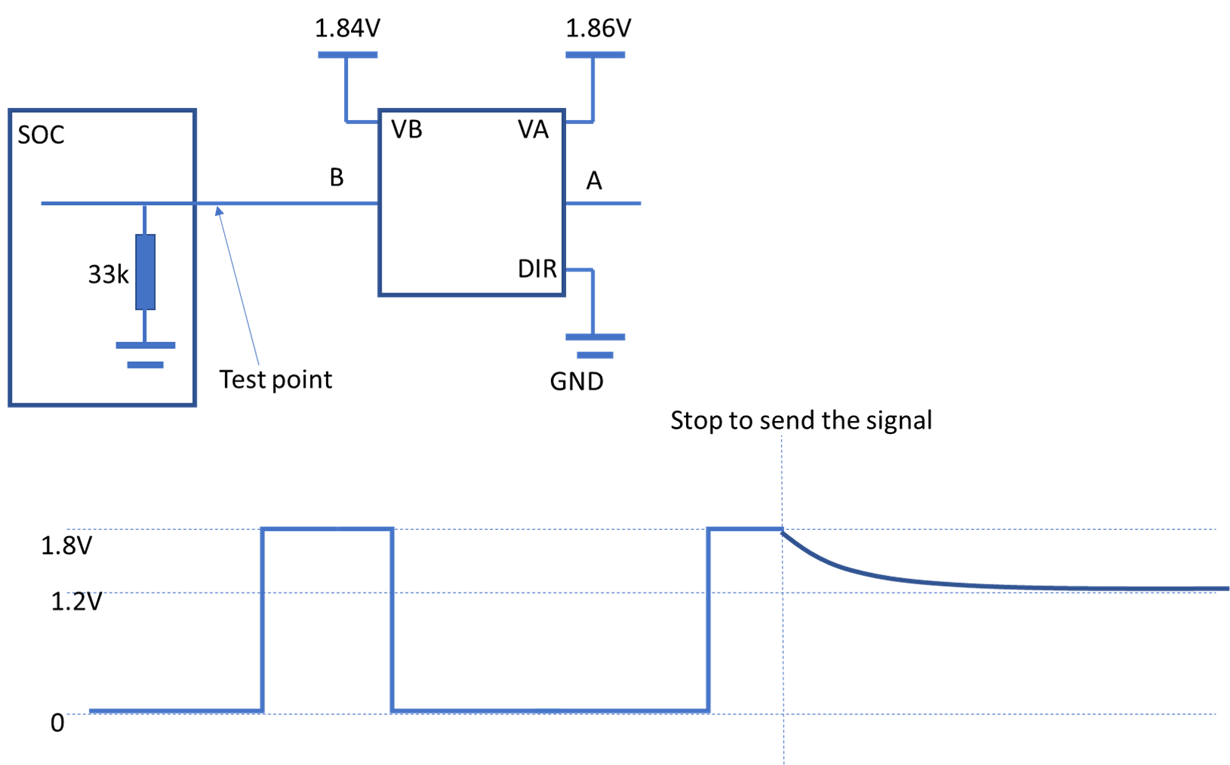

但是、如果它们未断开 SOC 和芯片、则测试点的电压将恢复到1.2V。 有关详细信息、请参阅下图。

如果我们将一个4.7K 外部下拉电阻器与33k 并联、则测试点的电压可返回0V。

我的问题是、为什么33K 下拉电阻器无法将输出拉至低电平?

B&R