主题中讨论的其他器件:CD404040B、 TINA-TI、 CD74HC4046A、 SN74LV4046A

您好!

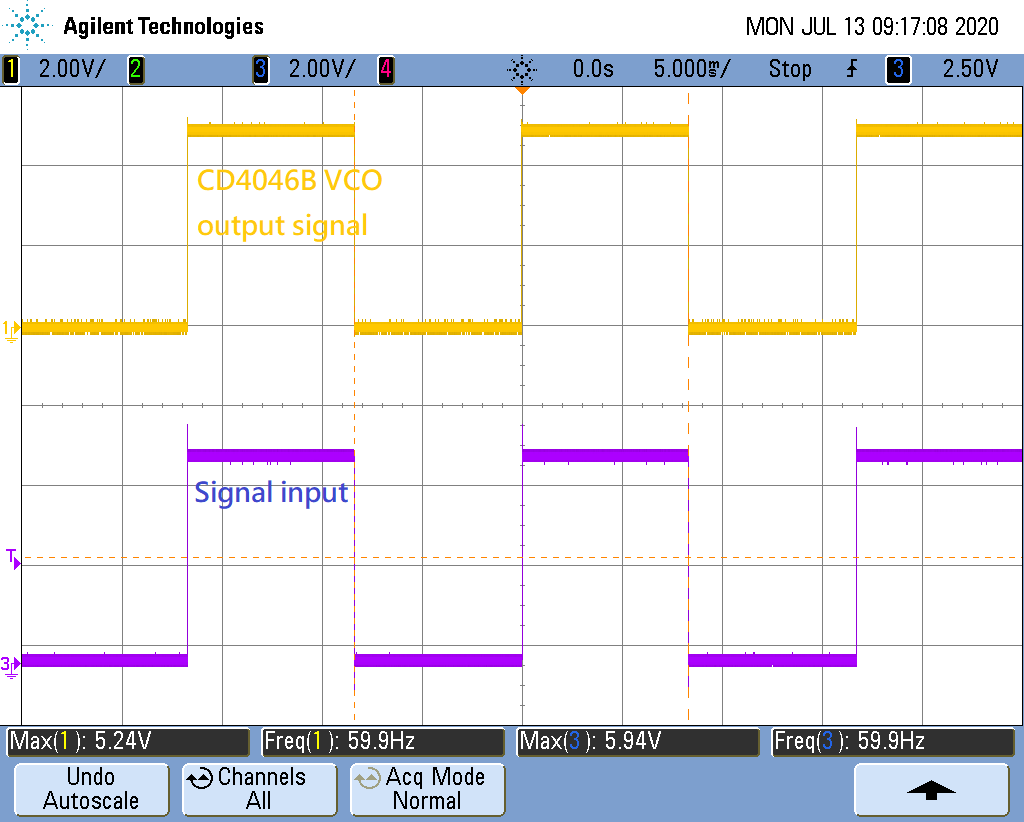

我想使用 PLL CD4046B 和 分频器 CD404040B 来设计60Hz 频率锁存器。

电路目标是锁定60Hz 信号。

我该如何开始?

请任何人与我一起解决这个问题。

提前感谢。

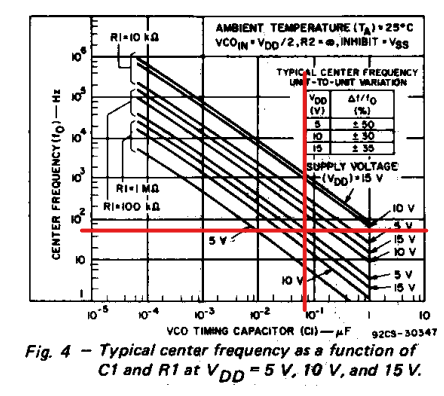

假设 VDD 为5VDC 且仅使用相位比较器1、则分频器 CD404040B 可除以1024或2048。

如何确定 VCO 输出频率以实现目标?

2.如何确定 R1、R2、C1和低通滤波器 R3、C2的值?

附加的是仿真文件、工具是 LTSpice。

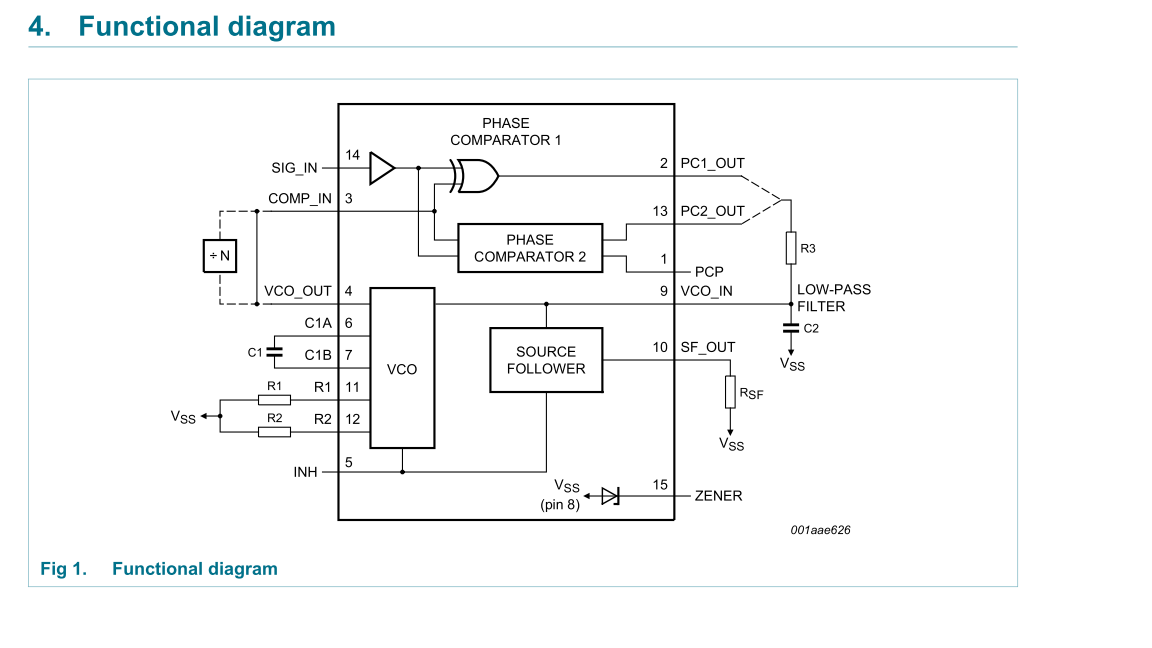

有关详细信息、请参见 HEF4046B 数据表。