主题中讨论的其他器件:TXS0102

大家好、

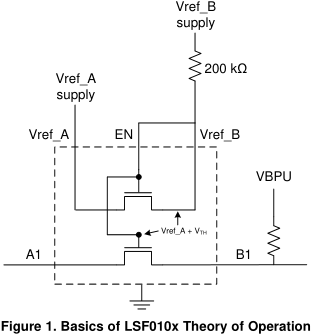

您是否有关于 EN 信号主动控制的任何指导? 具体而言、数据表指出 EN 需要连接到 VREFB、然后该引脚对通过弱上拉电阻标称值200K 欧姆拉至相关电源轨。 数据表还指示 EN 信号在驱动 LO 时将禁用器件。 因此、我认为 EN 信号只应由开路集电极或类似驱动器有效置位。 是这样吗?

我有两个用例、我认为这两个用例都很糟糕。

第一种情况是推挽驱动器主动驱动 EN 信号。 我相信、以这种方式配置的 LSF0102DGEQ 会很快损坏。

第二种情况是使用 FPGA IO。 FPGA IO 可以将信号 LO 置为有效以禁用 LSF0102DQEG 器件、然后进行三态处理以允许外部200K 上拉电阻器执行其功能。 我认为在这种情况下、FPGA IO 的弱内部阻抗往往会与 LSF0102DQEG 交互。 FPGA IO 阻抗因芯片而异、这往往会导致器件之间的行为不同。

谢谢。