https://e2e.ti.com/support/logic-group/logic/f/logic-forum/789519/cd4046b-cd4046b

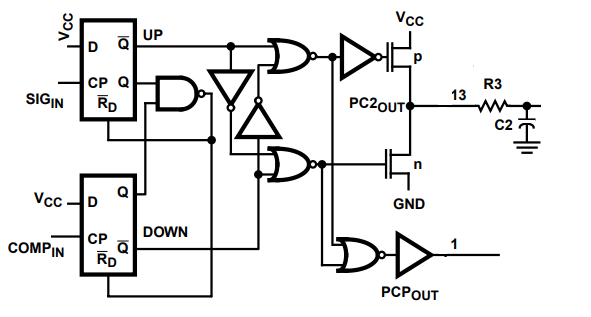

器件型号:CD4046B主题中讨论的其他器件: SN74LV4046A

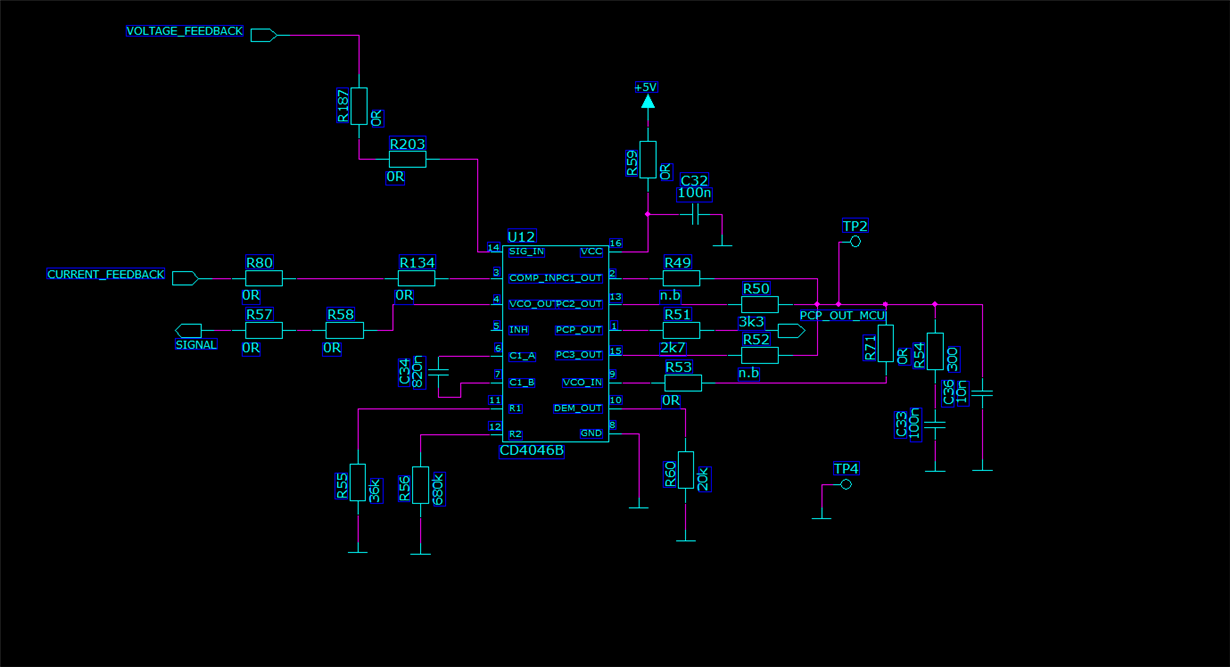

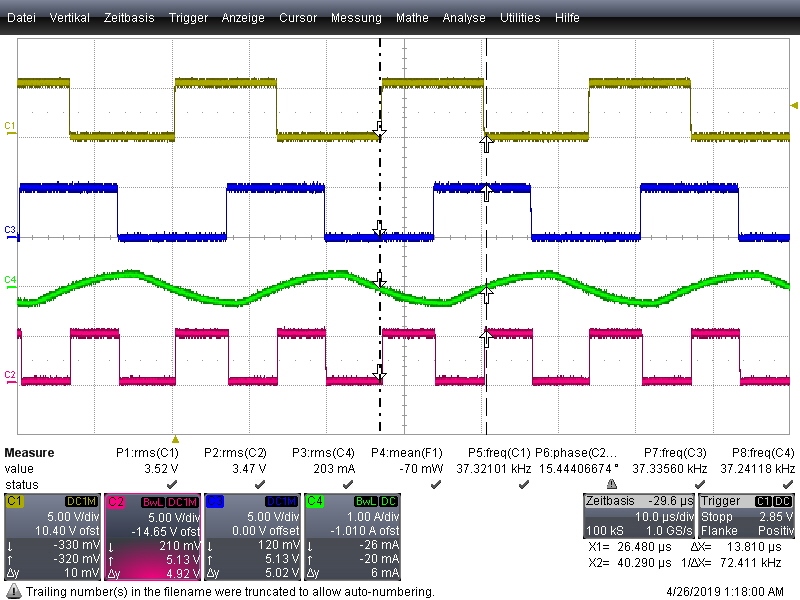

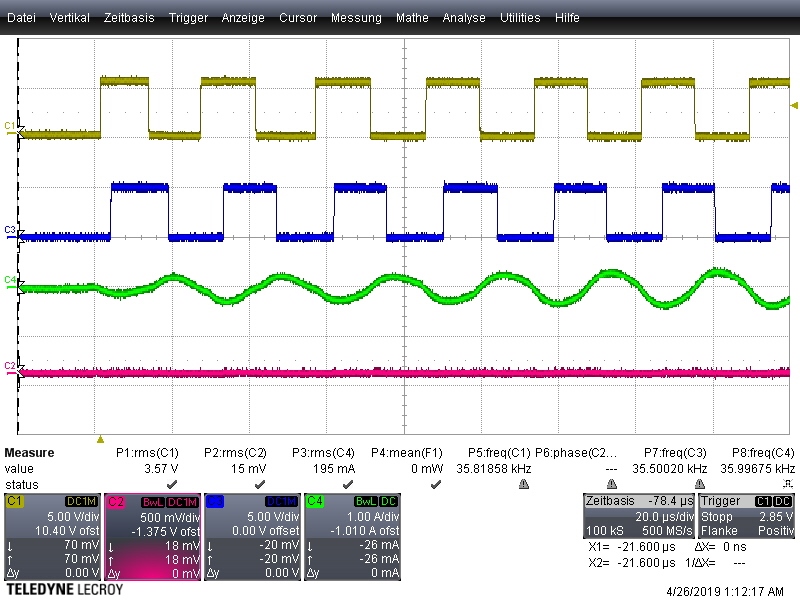

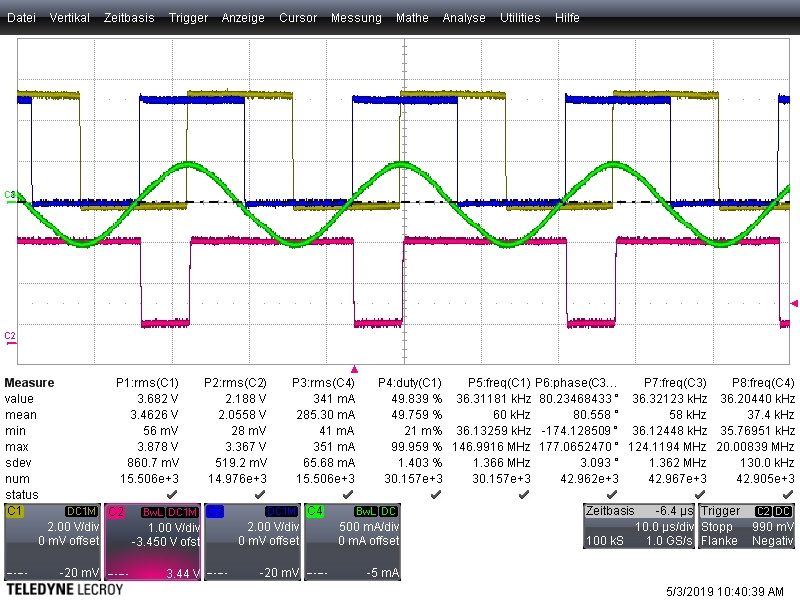

用于设置 Fmax 和 Fmin 的电阻器值不会为不同 IC 产生相同的频带。是否有一种方法可以在不同 IC 中以始终相同的频率从 fmf 获取到 fmin 的频带。 我的 fmin=35.4kHz,fmax =36,6kHz,一个1、2kHz 的电压。我使用的是680k 欧姆和36k 欧姆电阻,C =820pF。