主题中讨论的其他器件: SN74LVC1G17、 SN74AUP1G17

您好、先生、

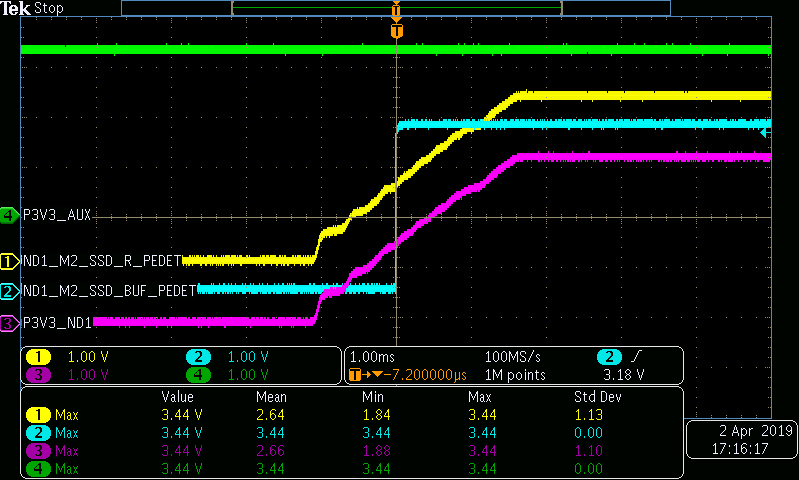

我们发现在波形下方的情况下有一些奇怪的峰值波形、

这可能会在客户方面造成一些问题、您能否帮助评论一下?

或者我们可以添加任何 权变措施解决方案 来避免峰值波形?

谢谢

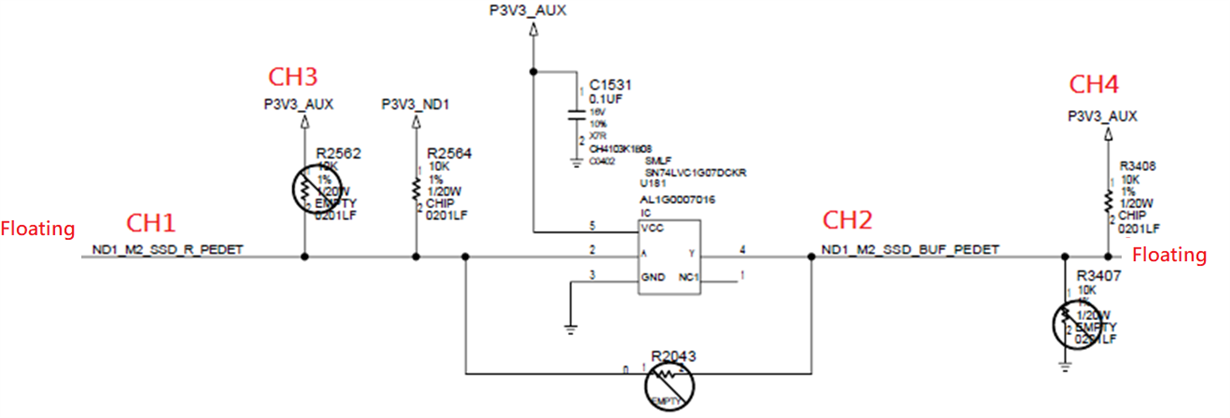

图1 是测量设置。

通道1:PIN2 (输入)

通道2:PIN4 (输出)

通道3:P3V3_ND1 (3.3V 电源轨)

通道4:P3V3_AUX (3.3V AUX 电源轨)

波形1。 当 P3V3_ND1 (CH3)导通时、SN74LVC1G07输出引脚4将从低电平输出到高电平输出

波形2。 放大波形1的 SN74LVC1G07输出引脚4 从低电平到高电平的输出

在 SN74LVC1G07输出变为稳定高电平之前、当 SN74LVC1G07 输入大约为1.6V 时、它将具有一些低于红圈的峰值波形。 每次输出从低电平变为高电平时都会发生这种情况。