https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1168101/cd4056b-pin1-6-7-description

器件型号:CD4056B需要清除3个引脚:

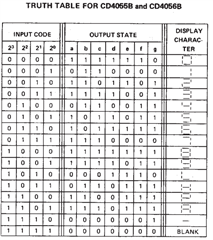

当引脚1 (Strobe)为高电平时、将输入直接推至输出、但 当引脚1变为低电平时、它将保持先前在显示屏中施加的输出。

4位输入引脚是否直接连接到~g 输出引脚?

引脚6 (中的 DIS FEQ)当为高电平时、输出 LED 将被视为低电平有效、但是当为低电平时、输出将为高电平有效

如果我们的7段显示 LED 是 共阳极、那么引脚6应该是高电平吗?

引脚7 (VEE)将是输出的低电平。 如果接地、当输出为低电平时、引脚7 (VEE)将为0V

当 VEE 为1V、然后输出低电平为1V 时、这意味着什么?

对于输入、这些引脚为高电平、我们是否应该添加上拉电阻器?

谢谢