主题中讨论的其他器件:SN74LVC1G17、 SN74LVC2G34

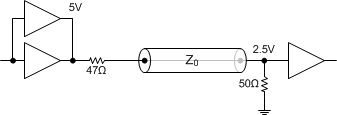

我尝试将以50MHz 运行的5V 时钟信号转换为以相同速度运行的3.3V 时钟、而不会将时钟反相。 我计划使用缓冲器、并由3.3V 电源供电、因此当我缓冲5V 时钟时、它看起来像是3.3V 时钟信号。 我开始使用 SN74LV1T126、我从产品页面中获取了 PSPICE 模型、将其导入到我的仿真器 LTSPICE 中、然后运行了仿真。 在没有负载的情况下、输入50MHz 时钟信号会在输出端以相同频率产生3.3V 时钟。 然而、当连接50欧姆负载电阻器时、输出要小得多、大约为1.86V。我搜索了与 SN74LV1T126相似的产品、我发现 SN74LVC1G17是一款类似的缓冲器、在24mA (3.3V 时)下具有较高的电流输出、 并且其时序特性与 SN74LV1T126相似、甚至不优于 SN74LV1T126。 时序很重要、因为时钟信号很快速、因此与 SN74LV1T126相比、SN74LVC1G17是否适合我的需求? 我本来会对它进行仿真、但我发现 SN74LVC1G17没有 SPICE 模型。