https://e2e.ti.com/support/logic-group/logic/f/logic-forum/592855/sn74lvc1g11-a-few-issues-questions

器件型号:SN74LVC1G11主题中讨论的其他器件: SN74LVC3G17、 SN74LVC1G97、 SN74LVC1G99、 SN74LVC1G123

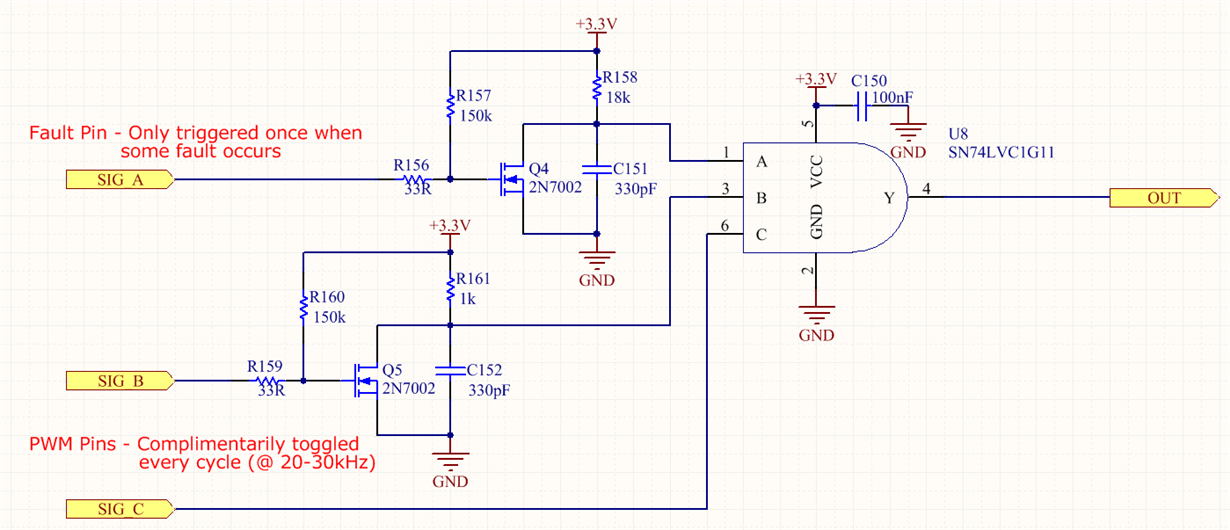

我有一个应用需要使用分立式逻辑来控制驱动器 IC 的输入。 一些关键标准包括在小型封装中仅使用一个 IC 和相对较低的传播延迟。 我选择使用 SN74LVC1G11 (单路3输入正与门)来完成任务。

请参阅随附的仿真/原理图。

此电路需要非常具体的行为、包括输入信号的反相和锁存(一段时间内)。 电路完全符合我的需求、但在构建第一个原型后、我发现了一些可能的设计问题(注意:不是从测试中、而是从数据表分析中)。

我 Δv、输入 A 和 B 上的 RC 延迟电路都违反了10ns/V 的"Δt μ V/μ s 输入转换"额定值 如果我正确理解3.3VDC 的 VCC、为了符合数据表图、我需要确保输入在大约33ns 内从0.8V 转换到2V。 这种理解是否正确?

信号 B 和 C 被切换至20kHz。 信号 A 很少切换-如果信号 A 变为高电平、则是一个故障引脚、用于将输出发送为低电平。 它旨在将栅极输出锁存到低电平几微秒(某种一次性行为)。

信号输入 C 正常-无违反。 信号 B 输入保持在0.8V - 2V 之间大约200ns、而信号 A 保持在瞬态状态几微秒。

这种情况是否会带来真正的风险? 我相信 VCC 电流不会有任何显著增加、也不会有任何额外的发热。 我也没有在测试中看到任何振荡。 我已经阅读了有关慢速输入的应用手册、但本文强调了在单个封装中存在多个栅极时的风险。 在这种情况下、只有一个门、对于我的分析、风险似乎很小。

如果我必须更改此器件、我假设我应该使用具有施密特触发输入的器件。 我找不到任何具有施密特触发输入的单路3输入与门、甚至找不到可级联的双路与门。 还有其他选项、请注意、我需要单栅极 IC 解决方案、并且更喜欢较低的总传播延迟。

谢谢