大家好、

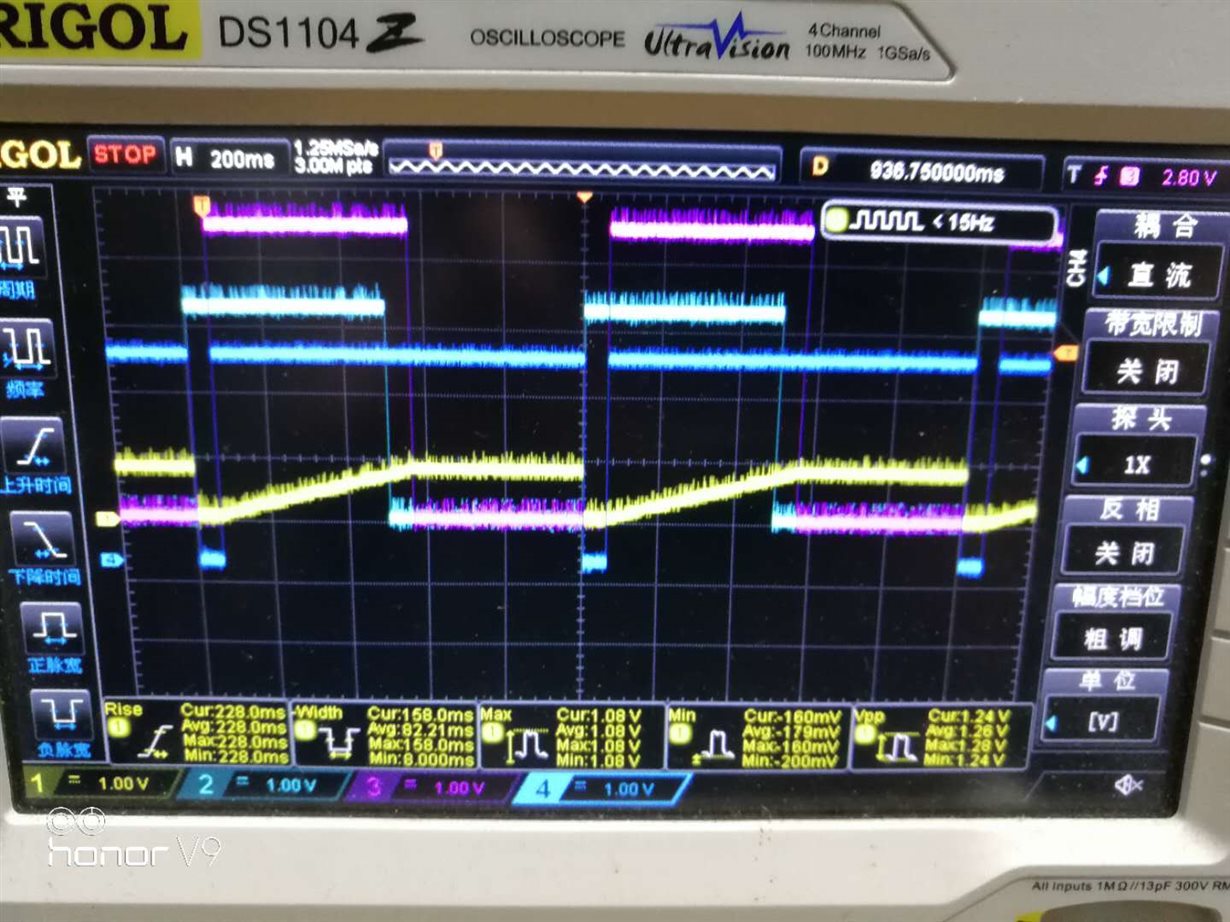

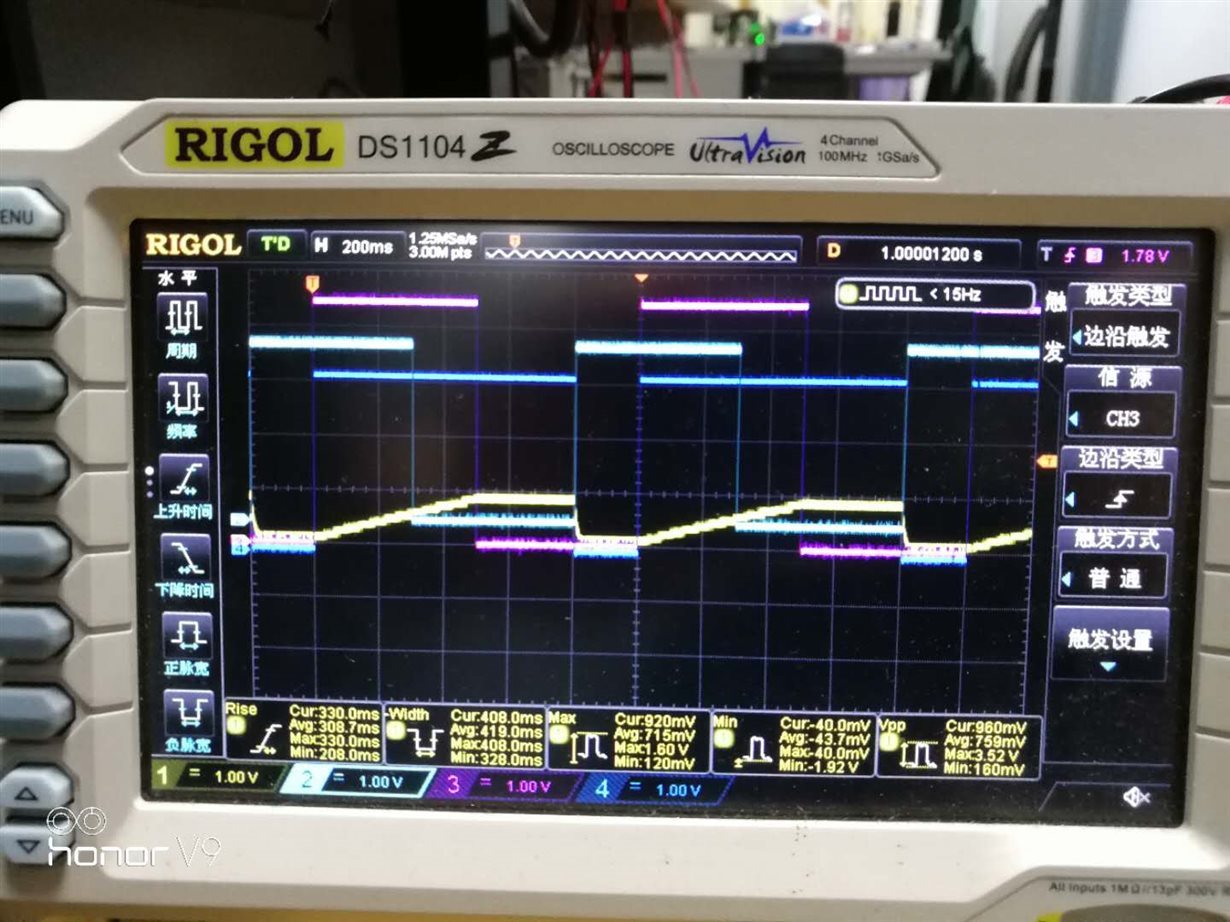

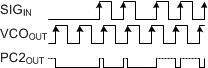

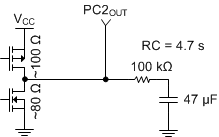

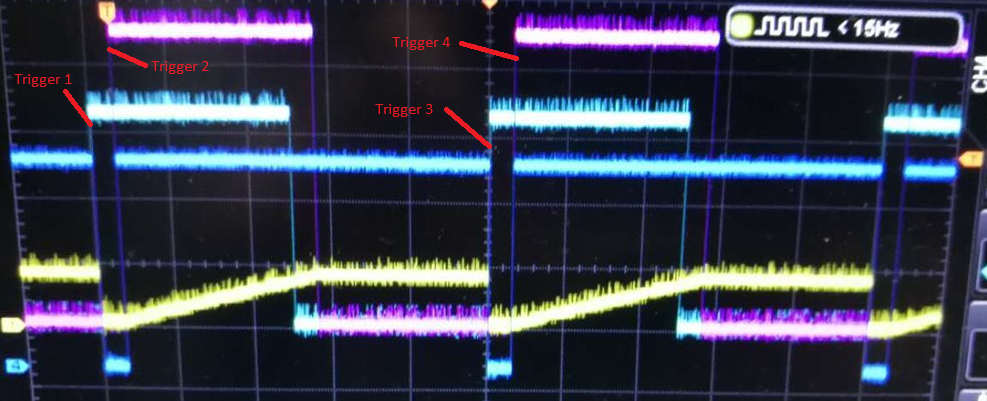

一位客户使用 CD74HC4046对 两个信号(1Hz)进行相位歧视。 他希望在滤波后利用信号 PC2out 作为 VCXO 控制信号。 当 PC2OUT 与任何器件断开时、可以明显看到相位歧视信号。 但是、当在 PC2out 之后连接 RC 低通滤波器时、相位歧视信号将消失、滤波器输出接近于零。

在正常情况下、滤波器之后的直流电压应接近1V、但不清楚为什么在连接 RC 滤波器后失去相位歧视输出信号。 RC 滤波器参数为 R=10k、C=10uF、因为输入是1Hz 信号、因此 RC 带宽非常低。

您能否解释可能导致此问题的根本原因并说明解决方法?

谢谢你。