大家好、

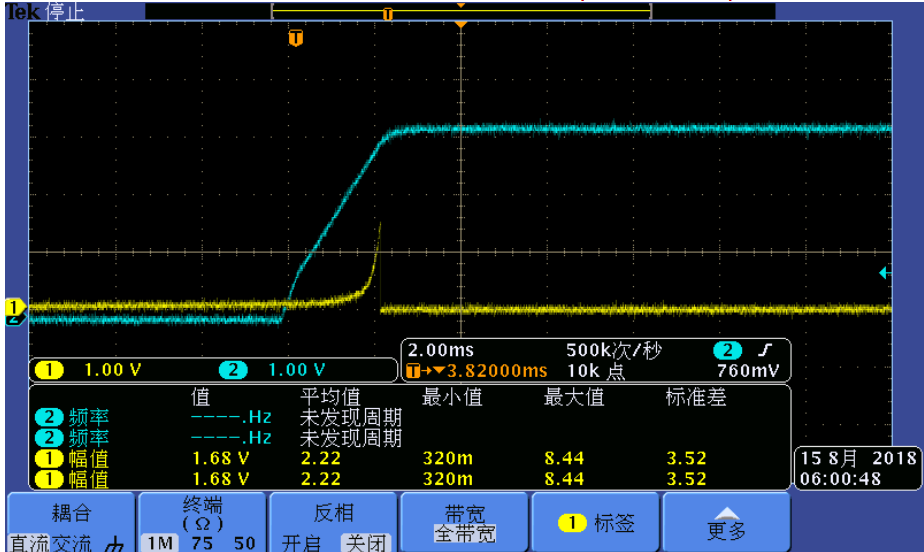

我的客户发现、当他们为 SN74GTL1655加电时、当电源电压达到大约70% VCC 时、会出现杂散。(请参阅下面的内容)

蓝色导通是电源电压、黄色导通是1A 输出信号。(下面是原理图)

电源的上升时间大约为2ms。

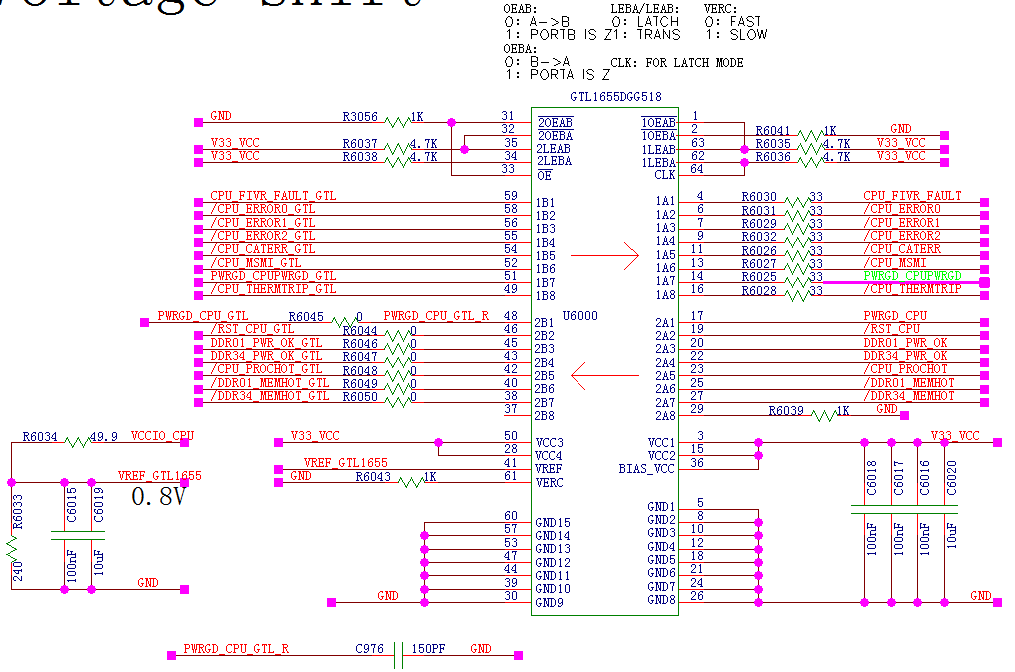

我的客户将1A 连接到 CPLD、并且有4.7K 上拉电阻器、并且 CPLD 引脚的输入电容大约为5pF。

因此、对于杂散、请帮助回答以下问题:

1.在上电过程中、是否是部件的正常性能? 如果不是、寄生信号的原因可能是什么?

2.您能否帮助分析是否有消除杂散的方法?

Lacey

非常感谢!