常见问题解答:逻辑和电压转换 > 输入参数>>电流常见问题解答

许多逻辑系统都需要上拉和下拉电阻器、以便在未使用连接到 CMOS 输入的导线时提供有效的逻辑状态。

简而言之、如果您不确定、请使用10kΩ Ω 电阻器并在遇到问题时进行调整。 答案很长。

主要关注的领域有两个:

(1)电流

(a) 驱动器拉取或灌入所需电流的能力

(b)泄漏会导致大电阻器上的压降

(2)转换速率-大多数 CMOS 输入需要最小输入转换速率、并且选择的电阻器将影响这一点。

(1)驱动电流

电阻器两端电压的调节公式称为欧姆定律、通常以 V = I * R 的形式给出

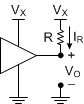

例如、让我们将一个电阻器从三态缓冲器的输出连接到 Vcc、通常称为"上拉电阻器"

当缓冲器的输出有效时、Vo 由缓冲器控制。

如果输出驱动为高电平、则 Vo = Vx、R 上的压降为 Vx - Vx = 0V、从而使 IR = 0。

如果输出切换到驱动低电平、我们首先假设 Vo = 0V、现在 IR =(Vx - 0)/R

根据驱动器的数据表、我们可以在给定此信息的情况下确定 R 的最佳值。 下面是 SN74AUP1G34数据表的快照:

选择3V 的电源值并知道2.7mA 驱动电流下的输出电压为~0.31V、我可以将上述公式调整为 :2.7mA =(3V - 0.31V)/R

Ω 并求解 R kΩ:R θ~= 996k Ω、或 R = 1k Ω、以获得更简单的值。

这不是唯一可行的电阻器值--理论上,我们也可以使用大于这个值的任何值,因为电流会减小。 MΩ、我们为什么不在每种情况下都只使用100 k Ω 电阻器来节省功耗?

一个原因是泄漏电流。 当缓冲器的输出处于高阻抗模式时,它将有少量的泄漏电流,这将在上拉电阻器上产生压降(V = I*R)。 如果电阻较大、则该压降可能非常显著。

另一个原因是导致延迟的原因、下一节将对此进行介绍。

(2) RC 时间常数

RC 电路需要时间进行充电。 上拉电阻器的全部用途是在不使用时将线路保持在有效电平、因此如果线路需要很长时间才能达到所述的有效电平、则会使该线路失去作用。

可以使用 t = 3*R*C 快速估算时间量

您可能会问"这个 C 的来源是什么"-这是线路上的寄生电容。 如果未给出、我们通常假设15pF、但您可以根据连接到线路的内容以及布线/传输线路类型的大小来确定系统的这一值。

假设您需要相当快的响应、最好保持 R 相对较低。 大多数 CMOS 器件对输入转换率有限制(通常在~20ns/V 范围内)、这会影响上拉电阻器的要求。