Other Parts Discussed in Thread: CD74HC04

您好!

我们使用的是 CD74HC04。 对于目前使用的正常产品、LO→Hi 和 Hi→Lo 的阈值没有显著差异。

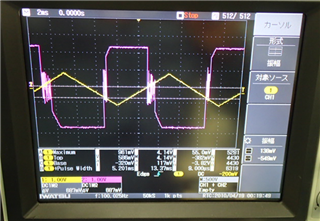

但是、所有新交付的芯片的迟滞约为700mV。 当输出电压从 Lo 变为 Hi 时、输入电压为-549mV。 此外、当输出电压从高电平变为低电平时、输入电压为138mV。

*由于产品的电源为±2.5V、因此高电平为2.5V、低电平为-2.5V。

这是符合数据表的规格吗?

[常规产品]

[具有迟滞的芯片]

谢谢、

Eevee