请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1195427/sn74aup1g74-can-clk-be-held-high

器件型号:SN74AUP1G74大家好、

客户希望在上电期间使用 SN74AUP1G74锁存信号。

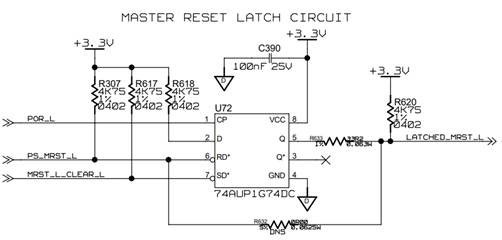

下面是电路的快照:

问题与器件时钟输入的上电复位信号连接有关。

在电源轨启动时、POR_L 信号将为低电平、但一旦所有电源轨稳定+~100ms 延迟、POR_L 信号就会变为高电平并在电路板通电后保持高电平。

使时钟信号从低电平转换为高电平一次(这将在逻辑1的 D 值中计时)、然后在之后持续保持高电平是否有效?

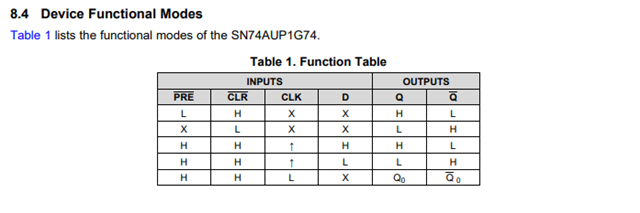

但将时钟保持为高电平可能不是问题、但不会显示为器件的功能模式之一(请参阅下文)

我们能否确认时钟始终为高电平的运行模式是否有效?