您好!

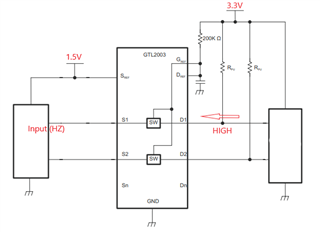

我想知道 GTL2003中的内部晶体管 在以下条件下如何工作。

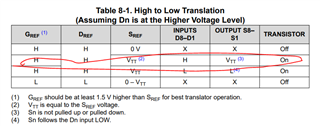

我已经检查了数据表中的表8-2、该晶体管的输出状态将是 VTT、晶体管将导通。 但我不明白晶体管如何使 Sn 达到 Vtt 电平。 您能否 详细解释一下晶体管的行为?

问题

1.您能解释一下在以下情况下晶体管打开的机制吗?

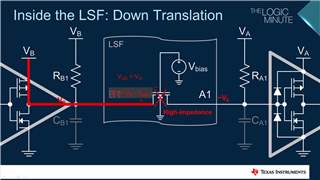

2.在输出端口(Sn)侧没有电压源(上拉电阻)。 当输入端口(DN)侧为高电平时、输出端口(Sn)如何使 VTT 电压电平?

3.如果连接到 DN 侧的器件使用 推挽端口、是否无需在 DN 侧使用上拉电阻?

Sn 侧上无上拉电阻器。

谢谢。