您好,

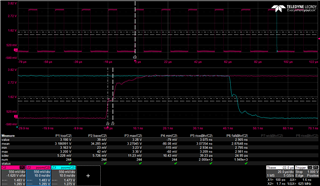

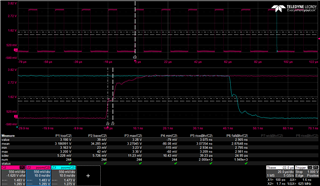

是否会担心边缘处的这一下降/阶跃? 我认为时间很短、不应产生额外的脉冲并影响以下器件。

您可以帮助确认吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

是否会担心边缘处的这一下降/阶跃? 我认为时间很短、不应产生额外的脉冲并影响以下器件。

您可以帮助确认吗?

这违反了 Δ V/Δ Δv t 限值(在 SN74LVC244A Δt 中缺失、但它仍然存在)、并且它接近 VCC /2、这实际上会导致输出端出现振荡。

到输入的迹线应正确端接;请参阅 LVC 设计人员指南的第47页。

尊敬的 Zach:

我要参考下面链接的应用手册:

https://www.ti.com/lit/wp/slla364a/slla364a.pdf

对于 LVC 系列、典型的最短上升时间将为10ns/V。