请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1286262/sn74lvc1g125-q1-design-bug

器件型号:SN74LVC1G125-Q1您好、TI 工程师,

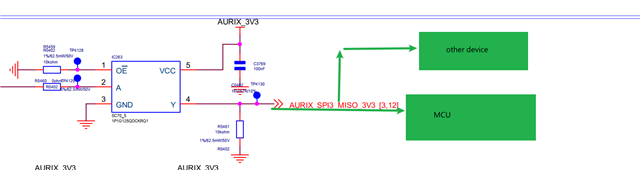

在我们的设计中有一个 SN74LVC1G125-Q1,OE 连接到 GND,且 A 来自外部器件(SPI_MISO), Y 连接到 MCU,我们发现、当 A 为三态时,Y 为低电平,但 MCU 无法控制 AURIX_SPI3_MISO_3V3 (该信号与其他芯片重复使用),我们想知道这是否合理,以及何时 将 A 下拉, MCU 是否可以控制该 Y 网络。