https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1319104/lsf0102-b-side-voltage

器件型号:LSF0102主题中讨论的其他器件: DRV8873

我写信是要询问您产品数据表表表表8-2中的陈述。 在该表中、提到了当 A=HIGH 时、"B 侧电压被钳位在 Vref_A。" 但是、我认为可能存在印刷错误、它实际上应该是 Vref_B。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1319104/lsf0102-b-side-voltage

器件型号:LSF0102我写信是要询问您产品数据表表表表8-2中的陈述。 在该表中、提到了当 A=HIGH 时、"B 侧电压被钳位在 Vref_A。" 但是、我认为可能存在印刷错误、它实际上应该是 Vref_B。

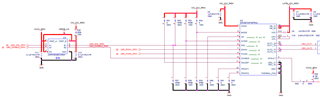

我写信来询问我在使用 LSF0102电平转换器设计电路时遇到的一个问题。 在我的电路中、我已经将 Vref_A 连接到3.3V 电源、并使用 FPGA 将 Aside 驱动至高电平。 另一方面、我已经通过200kΩ 电阻器将 Vref_B 连接到5V 电源、并将 Bside 连接到 TI IC (DRV8873HPWPRQ1)的引脚6 (NOL)。 但我注意到、Bside 的电压测量结果约为4V、这既不是预期的3.3V、也不是5V。 如果您能深入了解为什么 Bside 的电压与预期值不匹配、我将不胜感激。 LSF0102是否有任何特定特性或任何其他因素可能导致该偏差?