Other Parts Discussed in Thread: SN74LVC2G125

您好!

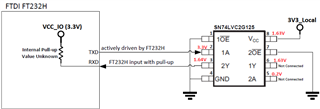

在一个电路中、我们使用 SN74LVC2G125作为 FTDI FT232H 器件的 UART 信号与我们自己器件之间的缓冲器。 一个用例是 切断 SN74LVC2G125的电源、同时 FTDI 芯片保持通电。 在这种情况下、SN74LVC2G125的 VCC、1Y 和2A 引脚的预期值应为0V。 但是、我测量以下电压电平:

断开 TXD 引脚连接没有太大影响。 但是、断开 RXD 引脚会产生显著的影响、所有其他相关引脚(VCC、1Y、2A)上的电压电平立即变为0。 尽管我不知道 FTDI 芯片的内部上拉电阻值、但我想它确实很弱、当未连接到 SN74LVC2G125时、悬空的 RXD 引脚只能测量到部分2.4V 电压。

我的印象是数据表中有关后驱动保护的声明恰好指这样的情况:

Ioff 支持带电插入、局部断电 模式和后驱动保护

这种情况是否对 SN74LVC2G125有害? 我有什么办法可以对付它吗?

此致、

克里斯蒂安

编辑:同时我也发现了 RxD 线上上拉电阻的值:介于40到190千欧之间,典型值为75千欧。 非常弱。