Other Parts Discussed in Thread: CD74HCT221, SN74221, SN74LV221A

主题中讨论的其他器件: SN74221、 SN74LV221A

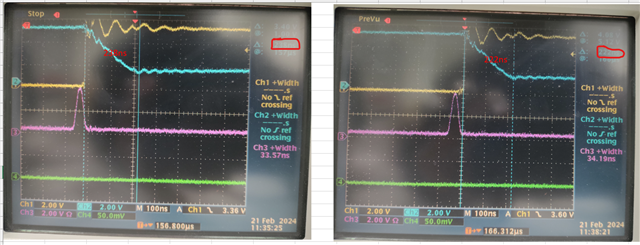

我的确将 U1 IC 从 SN74221NE4替换 为 CD74HCT221、其中一个原因是 SN74221NE4器件输出信号会根据输入触发频率发生很大变化。

与 TP32相关专门解决了一个问题、这与 CD74HCT221器件非常一致、TP32处的输出信号变化在8us 以内、而 之前的器件 SN74221NE4上的变化为~36us。

伸出的原因:在 TP27输出端,理论计算值与测量值不匹配(在第4点捕获),至少要有一定的理由,它不匹配。

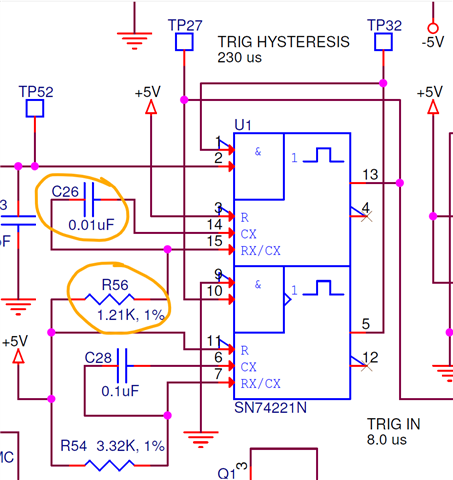

在以下电路中、在 R56 = 1.21k Ω 且 C26 = 0.01uf 的情况下、按0.7 x R X C 计算脉宽。

考虑到电阻器和电容器的容差、因此本文以粗体显示了 TP27最小值和最大值的理论计算

| 最小值 | 7.64E-06 |

| 典型 | 8.47E-06 |

| 最大值 | 9.34E-06 |

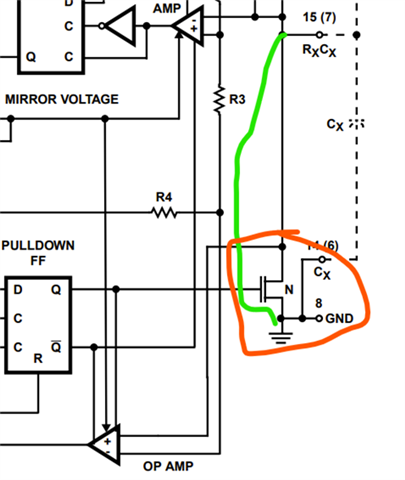

1.) 在裸 IC 上: 此 IC CD74HCT221上的 PIN6和引脚14 CX 引脚短接至接地 PIN8,这在功能图中似乎是预期的,一旦 通过内部 MOSFET 接收到触发信号,Cext 电容放电即可。

与之前的器件一样 、SN74221NE4 PIN6和 引脚14 CX 引脚没有对引脚8接地短路。

2.) 我正在尝试根据元件 R、C 容差以及 IC 输出容差本身来查看 TP27处的输出脉冲宽度变化

3.) 我认为 CD74HCT221 IC 具有2%的输出容差、在我的计算中、我考虑了7%(基于之前的器件 SN74221NE4数据规范)、这绝对不合逻辑、但 我可以根据反馈/注释将其更新为2%

| R56 | 1% TOL | 考虑 R 和 C 值的容差 | ||||||||

| 1210 | 12.1 | 1197.9 | 1222.1 | LN2 | R56 | C26 | ||||

| 0.7 | 1.21E+03 | 1.00E-08 | 8.47E-06 | |||||||

| C26 | 容差为2% | 0.7 | 1.20E+03 | 9.80E-09 | 8.22E-06 | |||||

| 1.00E-08 | 2.00E-10 | 9.8E-09 | 1.02E-08 | 0.7 | 1.22E+03 | 1.02E-08 | 8.73E-06 | |||

| 考虑 IC 本身的容差 | ||||||||||

| 最小值 | 7.64E-06 | 7.64E-06 | 7.88E-06 | 8.11E-06 | ||||||

| 典型 | 8.47E-06 | 8.22E-06 | 5.75E-07 | 8.47E-06 | 5.93E-07 | 8.73E-06 | 6.11E-07 | |||

| 最大值 | 9.34E-06 | 8.79E-06 | 9.06E-06 | 9.34E-06 | ||||||

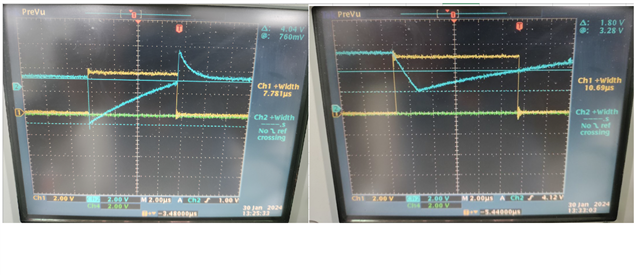

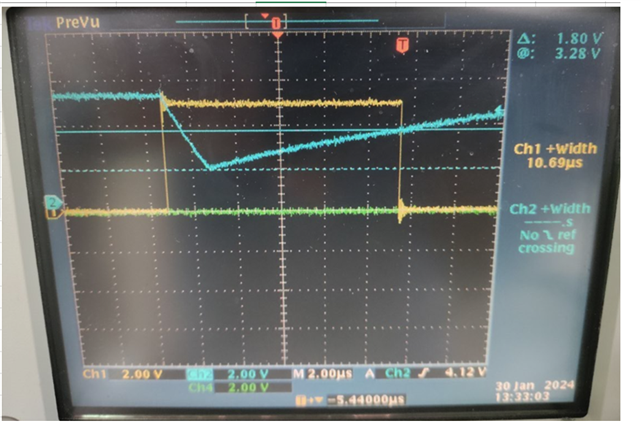

点4:TP27输出引脚处测量的宽度是10.69us?

总体而言、在 TP27上、该器件 CD74HCT221 的输出脉冲宽度为10.7us、而不受1至4kHz 触发频率(引脚2)的影响。

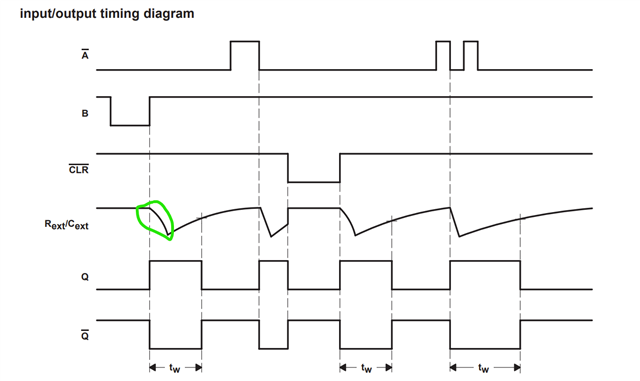

第5点: 典型的理论 计算电容大约为8.4us、这与电容器在第一个~2us 放电周期之后的充电时序几乎是匹配的

如何将此行为解释为 TP27的输出时序与理论计算值不匹配?

在以下情况下 、只要在引脚2上接收到触发信号、多谐振荡器输出 TP27 (Ch1)就 会变为高电平、并且 pin15 (CH2、蓝色)示波器捕获显示它开始 放电、一般来说、与本例中的~2us 相比、电容器的放电应该非常快? 对此有何评论?

在以下截屏中:CH1是 IC U1 CD74HCT221的 TP27引脚、Ch2 (蓝色)是 Rx 的引脚15 (CD74HCT221)

第6点:

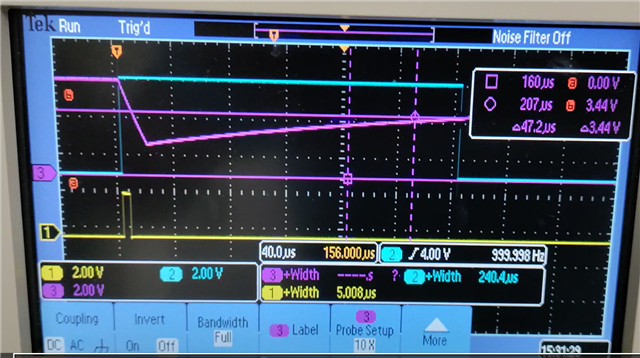

在下图中、我在多谐振荡器的第二部分中捕获了

Ch1是引脚2上的触发信号

CH2 (蓝色)是引脚5的输出信号、

CH3 (紫色)位于引脚7 (Rx / CX)

由于第二个多谐振荡器设置为230us、因此观察到的整体脉冲宽度为240us、其中观察到电容器的放电时间为~16us。

我不想混淆这个额外的数据集:-)。 看起来根据所设置的 RC 时序、放电时间会发生变化吗?

我无法在此窗口中粘贴图像,并在此请求的末尾附加图像,该图像被命名为第6点的图像。

总体而言、在 TP32上、该器件 CD74HCT221 的输出脉冲宽度+/- 8us 在1至4kHz 的触发频率之间保持一致。

| 最小值 | 233us |

| 最大值 | 241us |

第6点的图像