主题中讨论的其他器件: TXV0108、 TXS0108E

大家好、

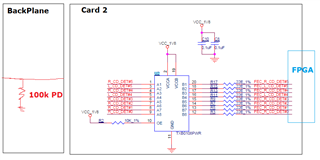

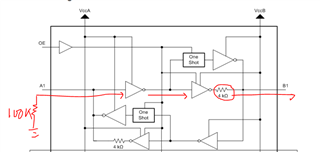

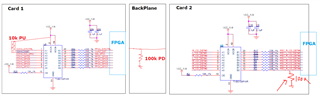

我在 背板中连接的两个卡之间使用 TXB0108作为缓冲器。 下面是我的电路。 两个 TXB 都连接到 FPGA、对于卡1、配置为 O/P;对于卡2、配置为 I/P。

我在卡1上有一个10k 的 PU、在背板(连接器卡)上有一个100K 的 PD。

电路的目的是检测/检测卡1是否已插入(存在)背板。

我在卡未插入背板时遇到问题、因为我从 FPGA 读取的是1、而不是读取0。 当我检查万用表时、我看到了1.714V 的逻辑高电平。

但由于 PD、它的读数应为0。 我很包容。 有人能帮我解决这个问题吗?