Other Parts Discussed in Thread: SN54SC6T17-SEP

您好!

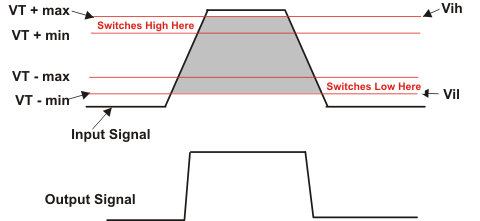

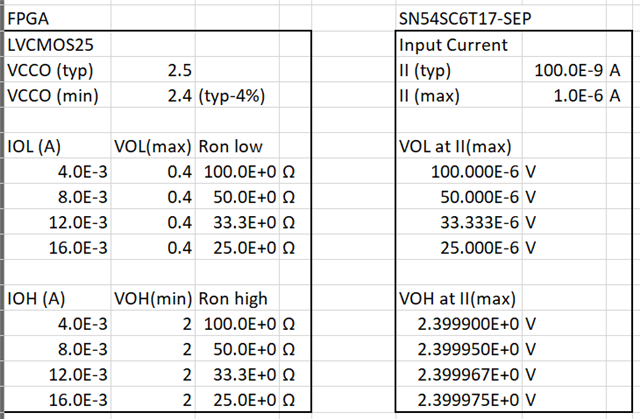

这是我的第一篇文章。 我正在使用 SN54SC6T17-SEP 进行设计、并尝试计算器件输入端的直流电平裕度。 我习惯使用一个表格、其中显示了 VDD 特定范围的 VIH (min)和 VIL (max)。 SN54SC6T17-SEP 数据表热心地提供了图7-2 SCxT 输入电压电平。 据我了解、VIH (min)用红色虚线表示、VIL (max)用黑色虚线表示。 TI 是否有以表格形式或拟合公式形式提供这两条曲线的文档、我可以使用这些曲线输入 VDD 和温度并获得 VIH (min)和 VIL (max)值? 第7.3.4节说"图7-2显示了 典型 VIH 和 VIL 水平..."这些曲线是否可在不同温度下获得?

例如、假设我想知道 VIH (min)和 VIL (max)在不同的 VDD 值下的电压:

- VDD = 4.75V 和5.25V、温度=-40至+85 C

- VDD = 3.15和3.45V、温度=-40至+85 C

- VDD = 2.45V 和2.55V、温度=-40至+85C

谢谢。

Rob