请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1349042/sn74lvc1g175-sn74lvc1g175

器件型号:SN74LVC1G175团队、您好!

我有疑问. 我们将使用该 SN74LVC1G175来控制 MOSFET。

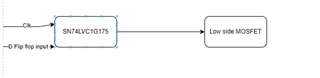

SN74LVC1G175的输出提供给 MOSFET 的栅极、如下图所示。

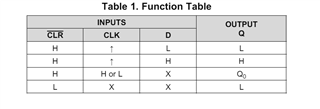

这里的问题是打开 MOSFET 和锁存触发器的输出,如果我们给一个上升沿信号在 CLK 右边应该是足够的? 我的意思是改变触发器的状态,一个上升沿是足够的,就不需要一个 PWM 类型的信号对吗?