Other Parts Discussed in Thread: TXS0102, TXS0108E

主题中讨论的其他器件: TXS0108E、 TXS010、 OS3

您好!

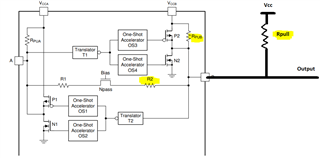

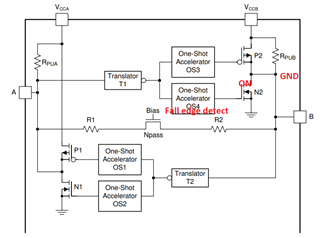

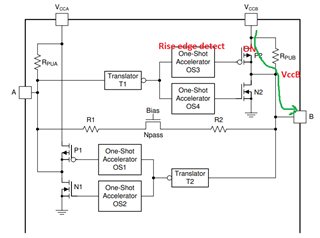

1) TXS0102和 SERIES 可以运行漏极开路和推挽模式。 但它是如何确定它驱动哪个接口的呢? 当我连接推挽式器件时、推挽式驱动器、当连接开漏式器件时、开漏式驱动器。 它如何决定是选择开漏配置还是推挽配置? 我阅读了应用手册和观看了视频系列、但我不明白为什么以及它是如何做出此选择的。

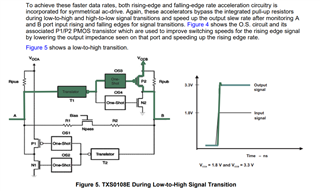

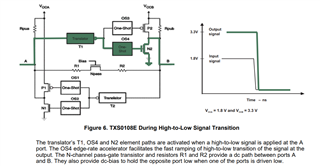

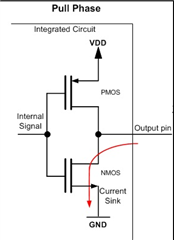

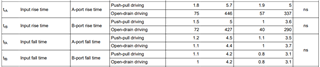

2) 我认为这个推挽结构可被用为一个开漏、在外部有一个上拉电阻器、(如果错误的话就予以修复。) 开漏支持的速度为2Mbps (2V5)、而推挽支持的速度为24Mbps (2V5)。 虽然我无法将 MDIO 接口驱动为开漏、但当我将推挽转换为开漏时、我可以驱动 MDIO 接口并使用它。 这种方法是否正确?

3) 3) 在 MDIO 接口上使用时、是否应该使用我要放置在外部的外部上拉电阻器来计算内部上拉电阻器?