https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1357541/sn74avch8t245-transition-timing

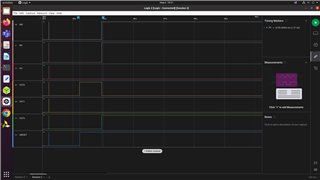

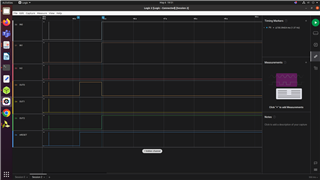

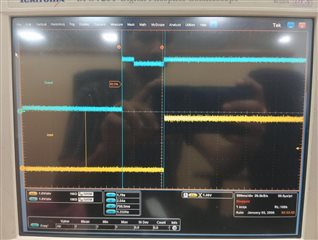

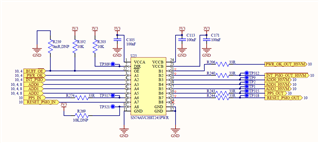

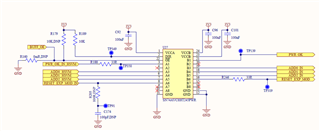

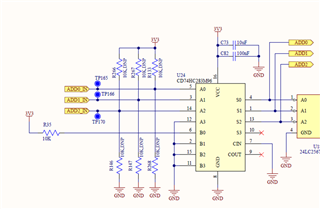

器件型号:SN74AVCH8T245您好、我们目前正在使用 SN74AVCH8T245 8位双电源总线收发器 、它具有连接至 VCCA 和 VCCB 的3.3V 电压轨、并将输出馈送到适配器(CD74HC283M96)、

我们的要求是使用输出位地址为100的总线收发器、并将此输入馈送到上述加法器 P/N、以及预期输出101、并将后续输出信号馈送到控制器。

但我们面临加法器输出不一致的问题、无法确定问题产生的位置、目前我们通过固件代码通过添加1秒的延迟和始终观察到的一致性来解决此问题、

我非常想知道硬件是否与任何东西有关、或者哪里出了问题、我要附上下面的电路图片。

如果需要进一步输入、

谢谢。