您好、TI 团队:

我对 SN74AHCT541DW 器件有疑问。

当我参考数据表时:

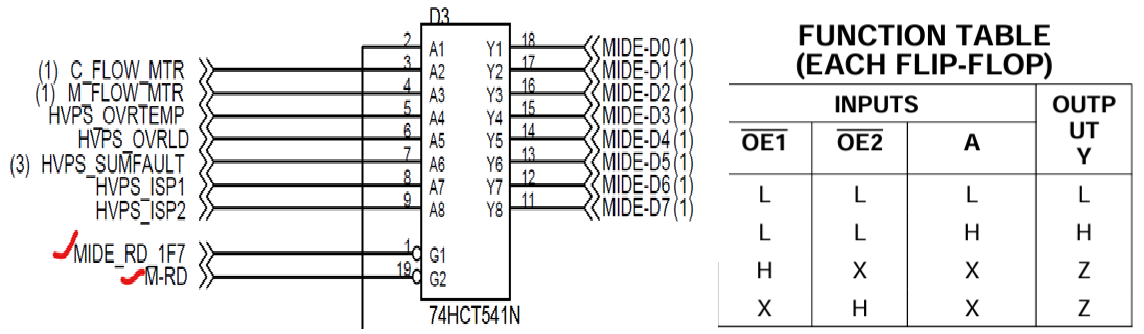

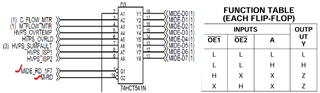

三态控制栅极是一个具有低电平有效输入的2输入与门、因此、如果任一输出使能端(OE1或 OE2)输入为高电平、所有相应输出均处于高阻抗状态。 当输出不处于高阻抗状态时、可提供同相数据。

为了确保加电或断电期间的高阻抗状态、OE 应通过一个上拉电阻器被接至 VCC;该电阻器的最小值由驱动器的电流吸收能力来决定。

我接下来的观察/问题可能是因为我们在 OE1和 OE2上没有上拉电阻器、当 OE1为高电平且 OE2在短时间内为低电平时、我们确实可以看到输出端出现瞬时低电平。

在我们的传统设计中、我们确实使用该器件。

最近、我遇到了一个 观察、虽然 设计发生在许多年前、这也是我将其称为传统的原因。

根据真值表、我看到 OE1和 OE2信号必须相互跟随、以确保只有当两者为低电平时缓冲器才有效。

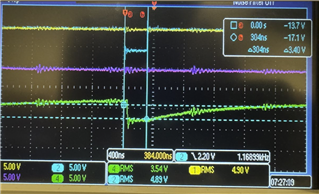

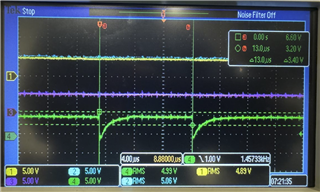

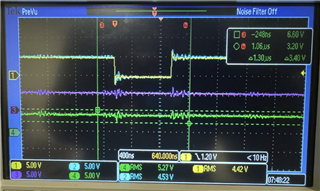

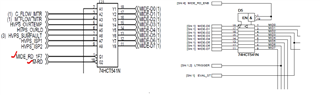

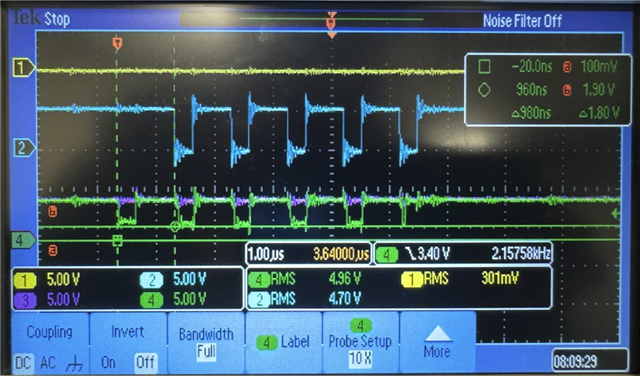

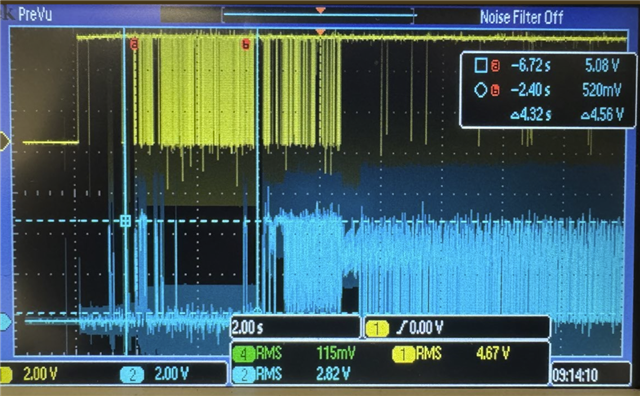

在以下示波器捕获中、

- CH1 (黄色):D3.1上的 OE1,在5V 电平下似乎是恒定的

- CH2 (蓝色):D3.19上的 OE2,当 CH2似乎以1ms 的速率切换时,它会在短时间内变为低电平,

- CH3 (紫色):VCC 在 D3.20上,我没有看到 VCC 电源线上的主要纹波

- Ch4(绿色): MID3在 D3.15, 有变化的 MID3信号输出,这可以误触发 HVPS OVR TEMP,我相信它取决于在低电平期间。

但如果您能解释为什么 MID3 D3.15信号在 D3.19低电平和 D3.1处于高电平状态时短时间改变其状态,这真的很有用吗?

是不是因为我们在 OE1和 OE2上没有上拉电阻器、我们在输出端确实看到了瞬时低电平(反相)、因为我们在设计中没有使用上拉电阻器设置高阻抗状态?

您能否确认我们是否以错误的格式驱动 IC、期望是同时驱动 OE1和 OE2为低电平、而不是间歇性(速率为1ms)、仅驱动 OE2为低电平?

此外、我将这视为引起误触发 HVPS OVR TEMP 信号的主要问题、即缓冲器的输入、MID3是缓冲器的输出。