https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1416225/lsf0102-leakage-from-bn-to-an

器件型号:LSF0102工具与软件:

嗨、团队:

我的客户(Len~ñ a)想了解有关 LSF0102的信息、如果 Bn 端口处于@ 0.7V ~低电平状态、该低电压是否会向处于低电平状态的端口泄漏?

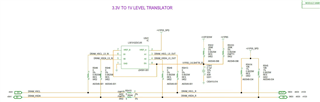

从 D/S 来看、如果任何一个为低电平(Bn 将泄漏到 A)、Bn 似乎直接连接到、但在英特尔最新的参考设计中、它们实际上使用此器件来阻止泄漏。 因此需要在此处进行确认。

谢谢!

Charles