https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1416978/sn74lv541a-output-topology

器件型号:SN74LV541A主题中讨论的其他器件: SN74ABT541B

工具与软件:

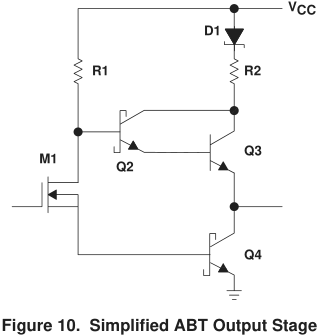

SN74ABT541和 SN74LV541的拓扑差异是什么?

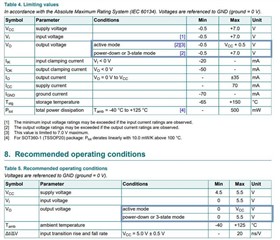

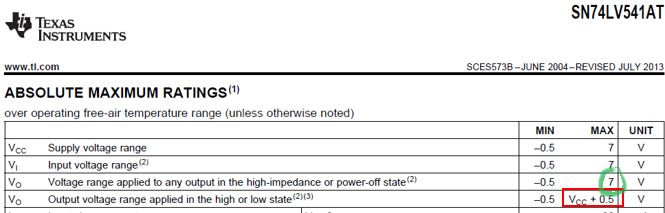

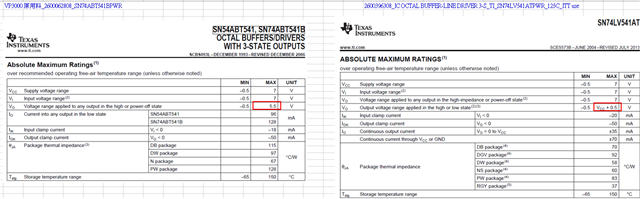

2. SN74LV541AT 的输出是否能够连接到高拉5V 电源轨? VO 的两个器件的绝对额定值似乎不同?

SN74LV541AT => VCC + 0.5V;当 VCC =~时、VO 降额仅为0.5V μ s

SN74ABT541B=>5.5V

此致

Brian