工具与软件:

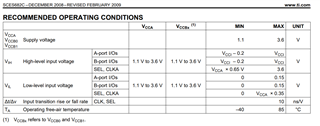

数据表未说明 B 侧3.3V 电源时的 VIH 最小值。

我有一个参考设计、其中 Xilinx Ultrazynq+可与 SD 卡相连。 在 FPGA 和该卡之间、我找到一个 TXS02612。 电平转换器在 A 侧具有3.3V 电源来满足 FPGA 的要求、在 B 侧具有3.3V 电源并连接到 SD 卡。

FPGA 中的引导加载程序可使该卡切换到1.8V 接口电平。 引导加载程序在 FPGA 中进行了硬编码、无法更改。 这意味着、我自己的没有 TXS02612的设计无法正常工作、因为 FPGA 的 VIH 最小值规格过高。

您的 TXS02612数据表未为 B 侧3.3V 提供 VIH 最小值。 我需要此信息、以了解其工作原理。

请指定这些值、并且有望更新数据表、

此致、Bo Bjerre