工具与软件:

您好、先生、

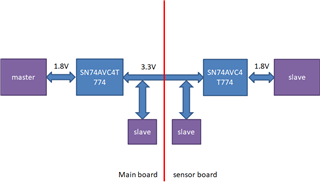

5MHz 的 SPI 时钟速率

您是否会 针对 以下 SPI 应用推荐 SN74AVC4T774?

在应用中、我们应该注意什么? 例如、负载电容

对于电平转换器的输入信号、您有什么要求吗? 例如、上升时间、下降时间等

谢谢

Hector

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、先生、

5MHz 的 SPI 时钟速率

您是否会 针对 以下 SPI 应用推荐 SN74AVC4T774?

在应用中、我们应该注意什么? 例如、负载电容

对于电平转换器的输入信号、您有什么要求吗? 例如、上升时间、下降时间等

谢谢

Hector