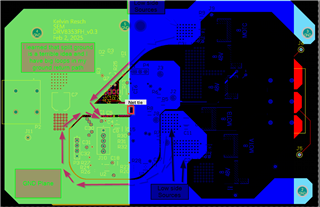

主题中讨论的其他器件: DRV8353、 CSD19536KTT、 UCC27301A

工具与软件:

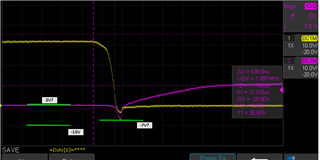

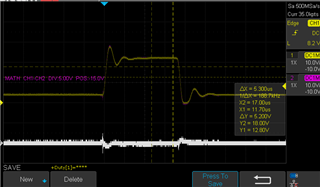

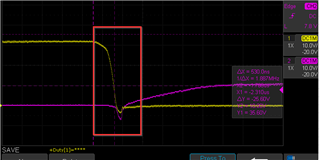

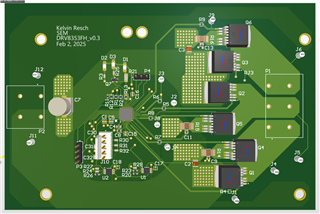

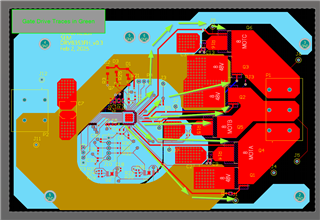

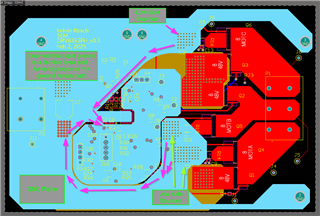

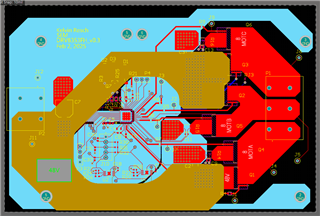

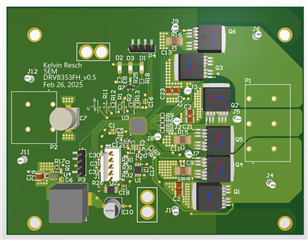

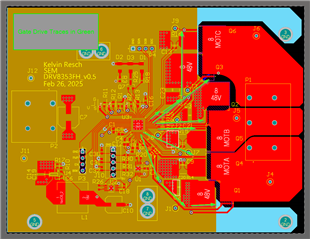

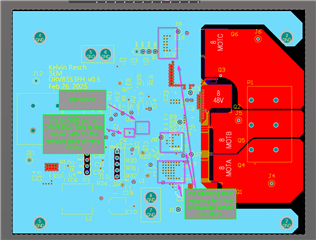

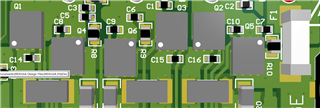

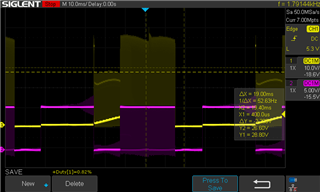

大家好、我希望你们做得好。 我对 DRV8353F 上的 BLDC 换向有疑问。 我将启动我构建的一个电机控制器。 它目前的运行电压为36V、这是在运行0.5A 电流下进行的示波器跟踪、但我最终将使其达到48V 40A。 在示波器图中、粉色是其中一个相位的低侧栅极、黄色是高侧栅极。

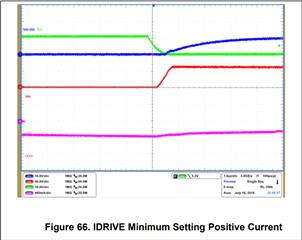

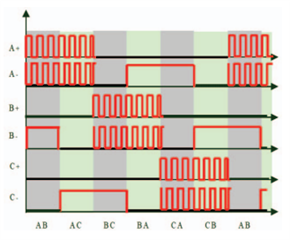

在 PWM 换向步骤之前、高侧栅极 PWM 处于较低电压、低侧栅极保持低电平。 根据我的理解、高侧栅极在此阶段不应该是 PWM 启动。 这个图表显示了我认为 BLDC 换向应该看起来的样子:

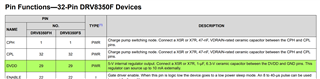

比如说在示波器中、我要测量 B 相。 我不明白为什么在交流换向阶跃(第二个)中、我的示波器捕获上的 B+看起来是 PWM。 我检查了其他两个相位、它们看起来也一样。 栅极线路应该是什么样的? 根据 DRV8353数据表第23页的换向表(表8-3)、我的高侧栅极在这个阶段不应该做任何事情。 此外、我怀疑这是霍尔传感器的问题、因为如果我在该相位处于换向状态、低侧栅极也将切换、但只有高侧栅极在这里切换。

我非常感谢您提供任何建议或支持。

感谢您花时间阅读本文档。

谢谢、

开尔文