工具/软件:

在采用块(6步)换向的三相逆变器(BLDC)和采用 Vishay TrenchFET、最大 VDS 为60V、总线为48V 时、我们的架构如下所示:

一个图腾柱为 PWM 模式(用于电源控制)、两个(高 FET、低 FET)互补切换、另一个图腾柱低侧为换向开关。

换句话说、在60度象限期间 a)灌电流低侧 FET 导通、而 b)源极通过互补开关进行 PWM 处理。

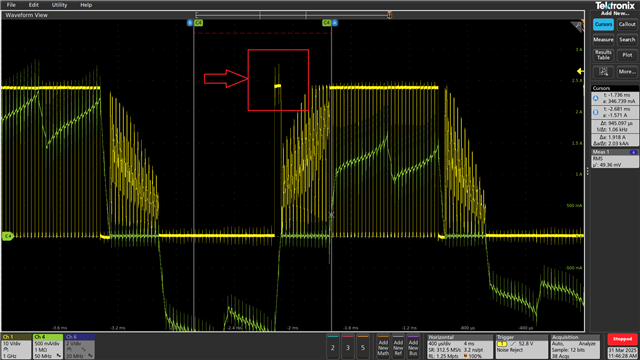

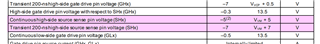

当下一象限接管时、灌电流(换向) FET 关断(例如 C 相)、其高侧 FET 体二极管开始续流、然后在短暂的软件延迟后、我们导通下一个灌电流极/相位(例如 B 相)的 FET。 在这段时间内、源极(例如 A 相)、当图腾柱 A 是互补开关高 FET -低 FET (避免击穿开关序列)时、当源图腾柱(A 极)在 C 相导通且现在关断(通过低 FET)时、瞬态会在总线以上~7V 的持续时间出现。 瞬态与 PWM-ing 具有100%的相关性。

无论我们怎么做、瞬态似乎永远不会超过~55V。它可以降低电压、使用不同的电机电流并降低栅极电流(IDRIVE)、但似乎非常奇怪的是、这种限制存在!!

我们认为、DRV 具有某种机制来分流 VM+7V 相位线上的瞬态(本例中为55)。 或类似的东西?

我们必须降低栅极电荷、因为55V 非常接近60V 最大 FET VDS。 我们已准备好发布该产品、但无法更改 FET。

这张图显示了两次瞬态、