工具/软件:

您好同事

在应用中、我需要一个半桥驱动器来控制外部锁定电机。 锁定电机的特性是正常电流5.5A (@200ms)和失速电流15A (@500ms)。

我想使用 DRV8244器件、并解答以下问题来支持您

1. DRV8244的输出引脚是否连接在一起来提高电流能力? 我只需要一个负载电流更大的半桥。

2.如果它可以在输出引脚连接在一起的情况下使用,电流能力如何? 它能否处理我在上方升起的锁止电机?

3.如果不能如上所述使用,您的建议是什么驱动这样的锁电机?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好同事

在应用中、我需要一个半桥驱动器来控制外部锁定电机。 锁定电机的特性是正常电流5.5A (@200ms)和失速电流15A (@500ms)。

我想使用 DRV8244器件、并解答以下问题来支持您

1. DRV8244的输出引脚是否连接在一起来提高电流能力? 我只需要一个负载电流更大的半桥。

2.如果它可以在输出引脚连接在一起的情况下使用,电流能力如何? 它能否处理我在上方升起的锁止电机?

3.如果不能如上所述使用,您的建议是什么驱动这样的锁电机?

谢谢

您好 Bing、

Unknown 说:1. DRV8244的输出引脚是否连接在一起来提高电流能力? 我只需要一个负载电流更大的半桥。

虽然这样做是可行的、但我建议查看 DRV8144 、以获得更好的解决方案。 如果您需要的电流能力超过 DRV8144可提供的电流能力 、我建议改用 DRV8145。

Unknown 说:2. 如果它可以在将输出引脚连接在一起的情况下使用、电流能力如何? 它能否处理我提出以上的锁定电机?

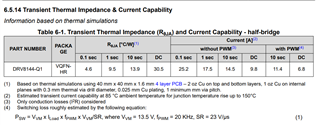

DRV8144可支持1s 的17.5A 电流、因此应该能够处理锁定情况。 如果您希望根据您的系统要求确定、可以使用我们的半桥结定子器( www.ti.com/.../SLVRBN2)检查 DRV814x-Q1半桥驱动器的热性能

此致、

Joshua

现在、我需要评估新功能的所有解决方案。

1.我确认 DRV8244可用作通过2路输出引脚连接的半桥以提高电流能力。 请问是否可以处理锁止马达(Nom. 5.5A@200ms; 失速15A@500ms)? 在设计中是否需要注意一点? 请分享您的意见。

2.对于 DRV8144器件、我已经让当地的 TI 同事检查价格。 顺便说一下、我使用"结温估算器"来评估热性能、但我找到了

a."转换率"和"VM"对热结果没有影响

b.对于 PCB 列表、我选择较大的 PCB 尺寸(8cm x 4cm)、热结果更差、但 PCB 尺寸更小(2cm x 2cm)、结果更好。 我可以知道原因吗?

您好 Bing、

让我仔细检查一下 DRV8244是否可以在并行模式下使用、热性能可能会比 DRV8144差、因为即使 IN1和 IN2连接在一起、一个 OUTx 也可能会先于另一个 OUTx 导通。

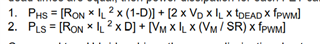

[引用 userid="624639" url="~/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1514288/drv8244-q1-drv8244-output-pin-connected-together-to-increase-current-capability/5822327 #5822327"] a."转换率"和"VM"对热结果没有影响这是因为仅考虑高侧 FET。 该应用手册包含计算器中使用的公式: https://www.ti.com/lit/an/slva504a/slva504a.pdf

因此、为了让 SR 和 VM 发挥作用、需要将电流输入设置为负值:

b. 对于 PCB 列表、我选择较大的 PCB 尺寸(8cm x 4cm)、热结果较差、但较小的 PCB 尺寸(2cm x 2cm)会获得更好的结果。 我可以知道原因吗?

这似乎仅适用于正电流、我不能太确定为什么看起来更小的 PCB 尺寸具有稍好一些的性能。 计算器利用 Foster 网络工作、因此中的某种因素会导致这种情况、但使用负电流时、热性能符合预期、较大的 PCB 具有更好的热性能。

此致、

Joshua

您好 Bing、

您说的是正确的。 由于 DRV8244没有并行模式、由于器件本身内的传播延迟差异会导致 OCP 故障或 TSD 故障、因此一个高侧 FET 可能会先于另一个高侧 FET 导通。 因此不建议将 DRV8244用于并联输出。

在支持并联输出的器件中、我们将提供一个可用的并行模式。 该并行模式改变发送到栅极驱动器的信号的方式、以便在内部为并联半桥提供相同的信号、以防止传播延迟差异导致击穿条件或一个 FET 在另一个 FET 导通之前导通、从而导致可能导致 OCP 或 TSD 触发的电流平衡问题。

此致、

Joshua