工具/软件:

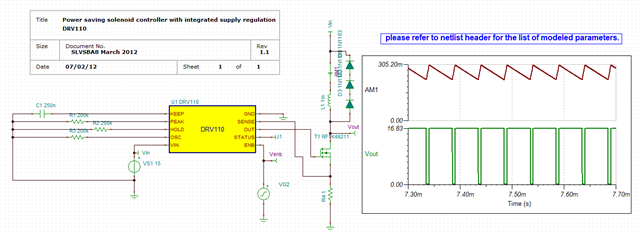

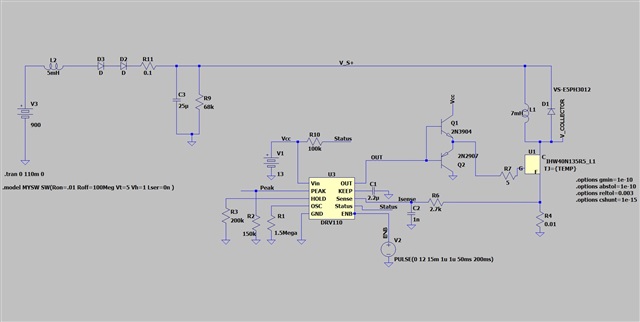

您好、我正在尝试在 LTspice 中仿真 DRV110、但模型中似乎有问题、实际上 PWM 的调节并不像 预期的那样、这里是测试电路:

。

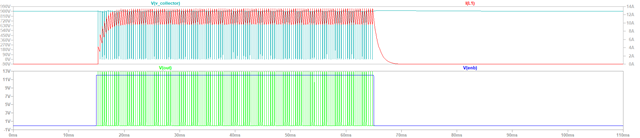

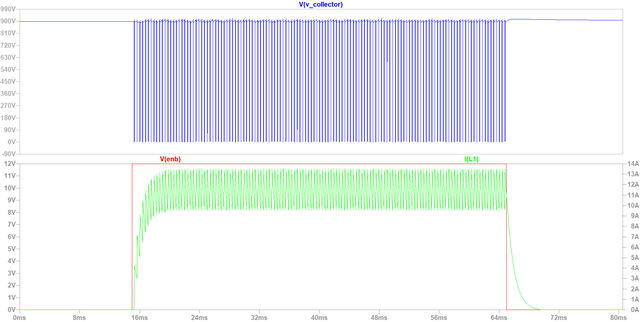

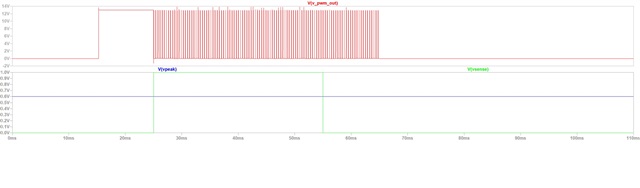

我们可以看到、当检测信号低于 Vpeak 电平时输出变为高电平、当检测信号高于 Vpeak 时 、DRV110 会将占空比降低到最大 10%、但当检测信号降至 Vpeak 电平时、dudty 周期不会变化并保持在 10%。

在模型库文件上:

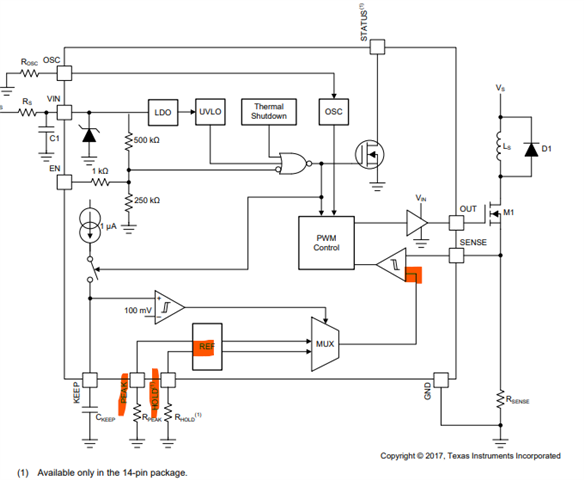

*如果 Vsense 小于 Vref、将生成高电平

* OUT 引脚。

*当 Vsense 大于 Vrefs 时、OUT 引脚 将生成一个* 10%占空比信号

出什么问题了? 如何解决?

谢谢

Antonio