Other Parts Discussed in Thread: DRV8305, DRV8305-Q1, DRV8305-Q1EVM, LAUNCHXL-F280049C

主题中讨论的其他部件:DRV8305、、 LAUNCHXL-F280049C

1. VCPH 电荷泵

客户想 知道 三倍频器模式和双倍模式下"PVDD、VCPH、CP1L、CP1H、CP2L、CP2H"的时序图。

他们想知道如何生成 PVDD+10V。

2.VVCPH_OVLO

应该是什么样的情况、VCPH 会超过14V。

3.VVCPH_UVLO2、VVCP_LSD_UVLO2

应该是哪种情况、VCPH、VCP UVLO 工作。

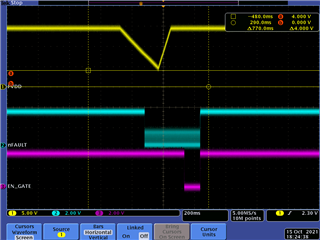

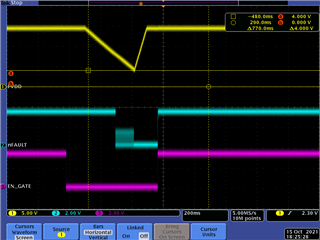

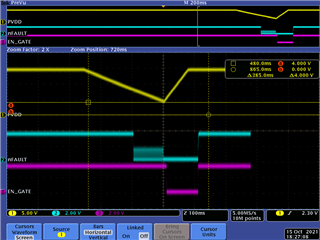

EN_GATE 和 nFAULT

当 EN_GATE 始终为低电平时、请告知我们 nFAULT 引脚在这种情况下的行为。

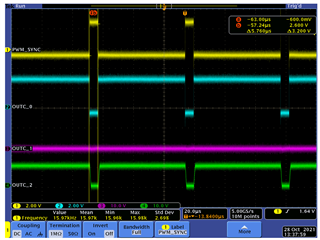

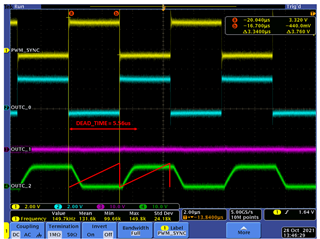

IDRIVE 的变化

请告诉我们 IDRIVEP_HS、IDRIVEN_HS、IDRIVEP_LS、IDRIVEN_LS 的变化。

6.VDS_OCP

请告诉我们 tBLANK、tVDS 的变化。

7.VDRAIN 引脚

请告诉我们 VDRAIN 引脚的灌电流大小。