TI 团队、

代表客户提出问题。

我刚刚注意到 DRV870x 芯片样片出现了一些意外行为、我恳请您提供支持、以确定根本原因。

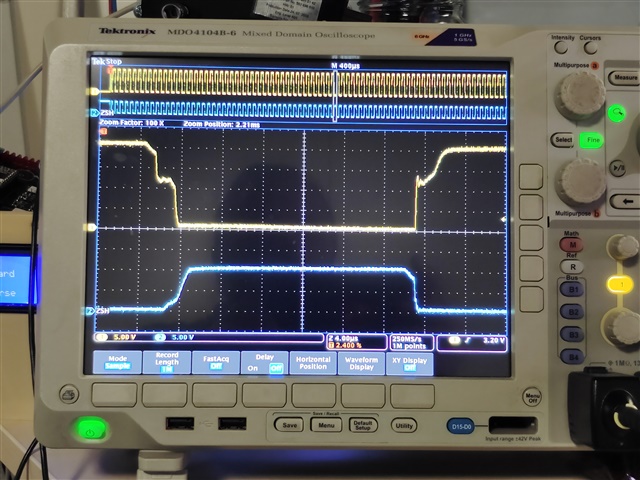

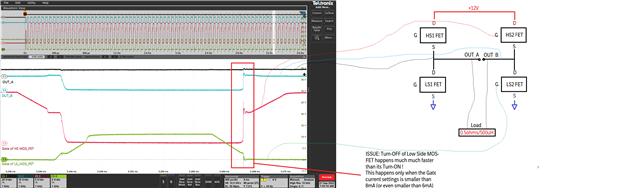

问题在于、如果栅极电流设置为<6mA、低侧 MOS FET 的关断速度会非常快、因此在这种情况下实际上没有压摆率控制。

有关更多详细信息、请参阅以下内容。

电流行为

电流行为

我注意到这个问题:

- 这发生在 TI 官方评估板上。

-针对6mA 或更低的栅极电流设置、出现在 LS2 MOS FET 上。 为此、我设置以下控制寄存器:DRV_CTRL_1 = 01010101 (对于 HS FET)和 DRV_CTRL_2 = 01010101 (对于 HS FET)。

-也发生在 LS1 MOS FET 上、但对于3mA 或更低的栅极电流设置。

-出现在 DRV8705和 DRV8706上(LS2的阈值与 LS1的阈值分别为6mA 和3mA);

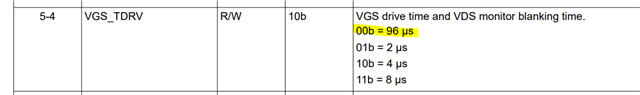

-无论死区时间设置如何(我甚至测试了8us 的最长设置)、都会发生;

-无论负载阻抗如何(I 测试的负载在0.5–10欧姆之间)、都会发生。

假设:

- 假设行为是由某些控制注册表设置引起的、您能建议我应该更好地检查哪些设置吗?

- 您能建议我可以进行的其他测试/检查、以找出此行为的根本原因吗?