您好!

我将使用不同的栅极电流进行测量。 当选择最大驱动电流(1A)时、低侧 FET 在启动期间会产生高栅极-源极电压。

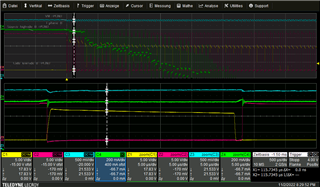

以下测量显示了低侧 FET 的栅源电压(黄色)。 第一个脉冲 几乎达到16V。 随着运行时间的推移、栅极-源极电压稳定下来。

只有在最大驱动电流设置下才能观察到这种行为。

您对影响的原因有什么想法吗?

提前感谢您的帮助。

此致

托比亚斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我将使用不同的栅极电流进行测量。 当选择最大驱动电流(1A)时、低侧 FET 在启动期间会产生高栅极-源极电压。

以下测量显示了低侧 FET 的栅源电压(黄色)。 第一个脉冲 几乎达到16V。 随着运行时间的推移、栅极-源极电压稳定下来。

只有在最大驱动电流设置下才能观察到这种行为。

您对影响的原因有什么想法吗?

提前感谢您的帮助。

此致

托比亚斯

您好、Akshay、

执行此测量主要是为了查看电子器件在最大驱动电流下的行为、而不是串联使用这些参数。

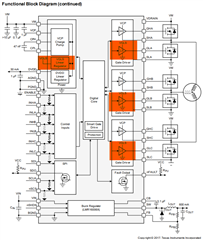

对于此问题、我想了解这种过压是如何发生的、因为我不了解数据表中的过压情况。 看一下、低侧栅极电压由线性稳压器提供。 该线性稳压器如何提供过压、以及该电压为什么会在几纳秒后降低。

要回答您的问题、有一张放大的启动时开关行为图片。 从2V 到20V、漏源边沿时间介于50ns 到150ns 之间。 VM 电源电压为22V。 在电流设置中、使用了两个并联 MOSFET、每个 MOSFET 具有8、3nF 的内部栅极和15nF 的外部栅极漏极容量。 单 FET 的栅漏电荷为34nC。

此致

托比亚斯

嗨、Tobias、

我认为亚伦的以下 E2E 可能能够回答您的问题。

此致、

Akshay

您好、Akshay、

感谢您提供 Aaron E2E 链接。

我知道跟踪电感会导致栅极-源极电压过冲、尤其是在使用高驱动电流时。 我不理解的是、为什么这些过冲不会持续发生。

这四个测量显示了不同的 IDRIVE 设置。

| 驱动电流 | 1000mA | 820mA | 680mA | 570mA |

| 灌电流 | 2000mA | 1640mA | 1360mA | 1140 mA |

|

|

|

|

当选择高电流设置时、栅极-源极电压达到15V 以上、并 在几毫秒内降至所需的约12V

假设原因是寄生电感、则电压过冲应是连续的、具体取决于所选的驱动电流、并且不会随着时间的推移而发生太大的变化。

此外、所附的测量结果显示 、即使栅源电压看起来稳定、也会出现随机电压峰值。

您认为这只是寄生电感、还是庇护了这种行为的来源。

此致

托比亚斯

嗨、Tobias、

您能否解释一下这些测量是如何捕获的、或者电机正在执行什么应用? 电机是在负载下运行还是在空载情况下运行?

为了弄清是否有一些寄生效应耦合到 GLx、我想查看相关信号:VM、SHx、GLx、相电流。

你们使用的是公共接地还是分离接地? 现在、如果有来自接地的噪声耦合、那么您能否提供 SPX wrt PGND 和 GLX 的波形?

此致、

Akshay

您好、Akshay、

在电机启动时在无负载的情况下执行测量、因此电机从零转至标称转速。

栅极-源极电压是在 FET 旁边的栅极-源极下拉电阻器上使用差分探针测得的。 直接在 FET 上测量漏极源极电压。 所有测量线均为双绞线。

电源接地和逻辑接地分离。 三个分流器位于低侧、低侧 FET 和 PGND 之间的每个相位对应一个分流器。

我将继续进行一些测量、直至星期三。

此致、

托比亚斯

尊敬的 Akshay:

您可以在下面找到进一步的测量结果。

| C1 | 黄色 | GATE 低侧_B -> PGND |

| C2 | 红色 | Source_highs端_B -> PGND |

| C3 | 蓝色 | VM -> PGND |

| C4 | 绿色 | I_PHASE_B |

| 驱动电流 | 1000mA | 570mA | 1000mA |

| 灌电流 | 2000mA | 2000mA | 1140 mA |

|

|

|

我还尝试单独降低驱动器和灌电流设置。

此致

托比亚斯

嗨、Tobias、

我们认为、这种行为是由于流入低侧栅极的高注入电流导致 VGLS 稳压器的电压升高、因为 VGLS 上没有内部灌电流能力。

这不是很常见、但高 IDRIVE 设置会在 LS MOSFET CGD 上耦合电荷。

您可以通过降低压摆率或在 GLx 和 GND 之间添加电阻器、以便在 LS MOSFET 导通时从 VGLS 吸收额外电流、从而减轻这种影响。

最棒的

Akshay

嗨、Tobias、

这是我们有关高功率系统的应用手册中的一个部分。 "这些下拉电阻的范围从数十千欧到数百千欧"

https://www.ti.com/lit/an/slvaf66/slvaf66.pdf

这些测试是否在极高的 IDRIVE 上执行以用于特定用途?

希望这一资源将证明是有用的。

最棒的

Akshay