您好、TI!

我对栅极布线的布局有一个问题。 我找到了一个用于计算宽耦合和边沿耦合布线电感的粗略估算公式:

显而易见、宽带耦合(方案2)布线的电感要小得多。 但我从未见过使用宽耦合布线的 PCB 布局、为什么会这样?

我能想到的唯一原因是栅极布线太短、因此并没有产生巨大的影响。 但如果布线较长(几厘米)、这将会有所不同。

我可以考虑的另一个原因是、以宽耦合形式对栅极布线非常不切实际、因为例如、在下面的这种布局中、我需要将顶层和底层用作电源平面(PVDD、GND)(以及其他元件)。 我认为、由于热分布、我不能将电源层放在内层上。

这些是原因还是其他需要考虑的事项?

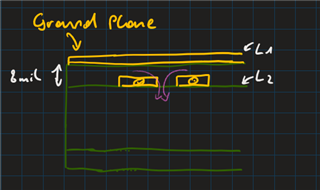

当栅极布线位于第2层、而顶层是接地平面时、栅极布线的电感会发生什么情况? (如下图所示)如果它要改变电感、低侧和高侧 FET 栅极布线是否存在差异?

你是否知道有一本书讨论了这类内容?

提前感谢、

但以理