您好!

我在从睡眠模式启用栅极驱动器 DRV8323时遇到问题、

我将使能引脚写入低电平以进入睡眠模式、此后、 我将引脚使能写入高电平但不起作用、电机的所有输出功率为24V、电机无法运行(我使用24V 电源)。

您能告诉我如何将 DRV8323从睡眠模式唤醒吗?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

为了满足唤醒条件、 当使能被写入高电平的时间达到 1ms 时、VM 必须大于至少5.4V 的内部欠压锁定条件电压。 您能否测量并提供 VM 和 ENABLE 上的电压波形、以及将 ENABLE 引脚写入高电平时 nFAULT 的状态?

您可以通过 在使能引脚上施加"高电平到低电平到高电平转换"来生成 ENABLE 复位脉冲、其中序列的低电平周期应该随 tRST 时间 块窗口下降。

希望这些信息有助于找到解决方案。

此致、

-约书亚

亲爱的 Joshua:

感谢您的支持。 唤醒栅极驱动器问题正常。

但今天、我突然检测到有关我的硬件 PCB 的一个问题。

我的设计使用 IC DRV 8323RH、因此增益输入引脚和 VDS 引脚在设计上有一个错误:

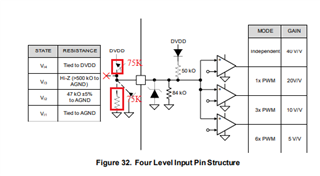

借助 增益输入引脚、我们在下面的图中插入了2分辨率75K 至 VDD 和75K 至 GND 行:

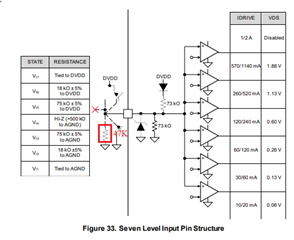

借助 VDS 输入引脚、我们将大小47k 插入到 GND、

我知道这是错误的,它不遵循数据表,我对2引脚的交换设计是错误的(它应该是 Hz 的状态为 VDS 引 脚的阈值= 0.06 ( 2分辨75K 到 VDD 和 GND )和47k 到 GND 的增益引脚(增益= 10V/V ) )。 但现在我们无法更改硬件 PCB、因为它是在密封箱中关闭的、我们可以将其打开。

因此、我们无法 通过真正的设计更改硬件 PCB、

我知道该 IC 在具有阈值的 V 输入电压引脚之间使用比较器、我们的设计错误、

V GAIN 输入= 1.88V

V DS 输入= 0.9V

如果设计错误、IC 的增益=? 且 VDS 阈值 =? 并对错误的设计承担任何风险?

BRS、

朗普特

您好!

经过考虑、我无法保证器件增益的性能超出预期和测试的引脚设置规格范围。

关于 VDS 阈值、它可能会在0.13- x -0.26之间浮动、您必须在器件上手动进行测试以确定确切的值。 尝试打开器件应不存在与其他潜在损坏相关的原因的问题。

为了获得理想性能和预期性能、我最好的建议是在设计 PCB 时考虑正确的配置。

如果不可能、我会继续测试您的器件输入/输出、以确保没有受影响的参数违反 ABS-MAX。

此致、

-约书亚

Joshua、

感谢您的回复。

那么增益是不是等于20、我已经测试并发现增益是20。 我进行了测试并得到 V Gain 输入> 1.726V、增益为20。 在我的设计中、V 增益输入= 1.88V、因此是20。 但我想知道是否有任何情况下,增益可能从10 - 20像你说的 Vds 阈值浮动,如果增益值可能浮动,这对我来说是一个大问题,如果是常数20,那就可以了。

使用 VDS 阈值如果可能在0.13至0.26V 之间浮动、并且只会 影响电路板的保护电流阈值(= VDS 阈值/ RDS_MOSFET)、只要不影响 IC 的其他元件、我认为是可以的。

请确认我、在本例中、增益是否为常数20?

BRS、

您计划的标称电流是多少? [/报价]-->我的应用程序的额定电流为3A。

[/quote][/quote]VDS 阈值能够降低到0.06V,但这同样需要更改设计。 [/报价]-->是的,设计变更是新一批产品的必要条件。 但是对于集成产品、我决定不修复电路板、因为它仍在正常工作、目前在相位测试期间、我们未检测到任何驱动器问题。

[/quote]由于异常配置,如果增益完全浮动,则更难确定其位置。 在您看到的已知20V/V 增益之外、我不确定器件运行期间引脚的灵敏度、不认为很容易给出建议。 [/报价]出于这个考虑、您能否与专业水平更高的电机驱动器 DRV8323合作提供建议?

BRS、