主题中讨论的其他器件: DRV8955

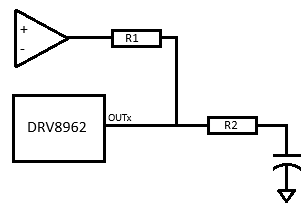

大家好。 我们有一个非典型应用 、该应用使用 DRV8962和功率运算放大器来驱动容性负载。 DRV8962输出和运算放大器输出与容性负载并联、并且在 DRV8962和运算放大器之间有一个电阻器。 请参见下图以了解一般连接。

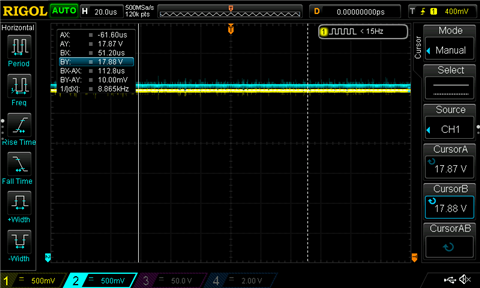

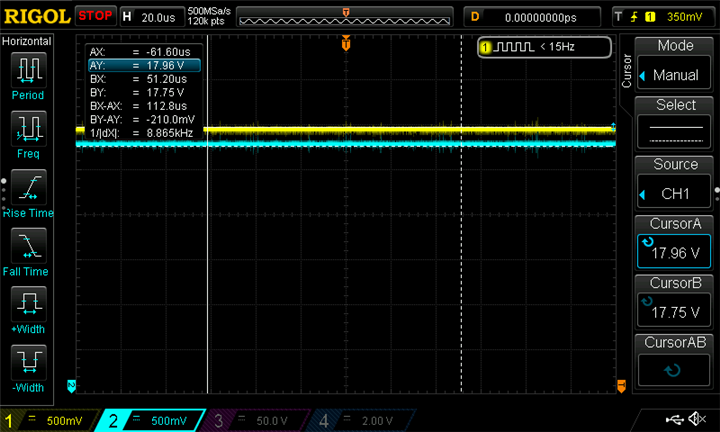

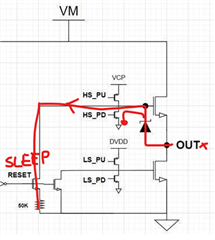

一般来说、此设置正常工作。 运算放大器控制容性负载的大部分输出信号、而 DRV8962在某些信号转换中触发高电平或低电平 FET。 当容性负载保持在稳态电压时、DRV8962将被禁用(ENx 为低电平)、并且运算放大器保持输出电压。 我们面临的问题是、在该状态下、R1上出现了大约0.2V 到0.5V 的压降。 这会在 R1和运算放大器上引起不必要的散热。 由于电容器此时已充满电、因此阻性负载的唯一来源是 DRV8962处于高阻态。

此外、如果我们将 DRV8962置于睡眠模式、将 nSLEEP 驱动为低电平、则会消除电阻负载、并且 R1上没有压降。 多余的热量得以消除。

R1上的稳态电压和压降之间的关系不像我预期的那样呈线性、因此我们在确定 DRV8962的电阻负载时会遇到一些问题。 您是否有关于禁用时 DRV8962输出信号行为/阻抗的任何详细信息? 我们无法在数据表中找到任何详细信息。 谢谢。